|

|

Forum Index : Electronics : Inverter Choke Design Discussion

| Author | Message | ||||

| rustyrotors Newbie Joined: 07/01/2023 Location: United StatesPosts: 36 |

i had the same question a while back, but did not get many replies. here is the process i used to design my choke, but it could be all wrong.. i figure we are designing a low pass 2nd order filter consisting of choke inductance and the output capacitor equivalent capacitance at the primary. so i start with the midpoint between our two switching freqs, 50/60Hz and 24kHz, as the filter cutoff freq, which is roughly 1100Hz. i think if the design cutoff freq is too low, you end up with reduced efficiency at high loads due to passband loss. if its too high, less efficiency at low loads. so i used 1100Hz as filter cutoff design freq to find a rough target choke inductance, ends up being somewhere around 30uH. experimentation shows that is about where idle power reduction starts to level off as choke inductance is increased. aim a little low to account for transformer leakage. then use choke core material datasheet AL value to find core material, number of turns, and how many cores to stack to get the target inductance. core datasheet should have plots of either initial permeability vs magnetizing force or AL vs Amp*Turns. permeability is directly proportional to inductance, so you can use those plots to see how much inductance drops with DC current. in general, lower permeability cores will lose less inductance as current increases, but you will need bigger cores to get your target initial inductance. higher permeability cores high inductance will save you some space, but inductance will drop off fast with current. then i used peak current to find core loss. so peak current would be max load (W) * sqrt(2) / [13V (24v inverter) or 26V (48v inverter)]. from that, find magnetizing force, flux density, and then core loss using datasheet plots and equations. from the core loss plot, i only use the 60Hz line. i figure 2nd order LC filter will have 40+ dB attenuation at 25kHz, current and core loss at 25kHz will be very low and negligible for decent materials that method seems to match the results. i initially was using -26 powder iron cores, but they got way too hot due to excessive core loss. sendust cores have much better core loss, usually under a few watts at full load. i ended up with a 4-stack of sendust 250125 (2.5in diameter, 125 permeability), based on size constraints, cost, and availability. i think i found them in the US on ebay for $20/ea. this choke with 4 turns makes about 25uH at idle and theoretically drops to about 9uH at 3kW load on my 24V inverter Edited 2024-01-29 15:03 by rustyrotors |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Nicks, Phil & Pete this post is to answer the bits of "input" I have received re inverter choke design, in doing so I have helped in my own sanity check query. My labouring on the choke design issues is that for anyone trying to read and understand the issues it is better to break them into bite size chunks and not throw a heap of less relevant and gut feel issues that only serve to cloud and complicate something that eventually becomes too difficult or impossible for anyone to solve. My skill for switchmode design has served me well in my career and the company I started and ran for nearly 20 years before selling it. Our first design was for 2 racks of 128 Battery formation chargers using 120VDC input, each Eurocard Hot Swap 2kW capable (buck switchers) for Exide Adelaide that handled 245kW total and was extended by another 512 to finally involve over 1MW and ran 24/7 for over 15 years with just a few units needing service. And I used similar formulas I will present shortly. As a footnote the design/install engineers at Dunlite who did the physical installation and rectifier connections said the racks will just melt down & they would never work - I am used to scorn, but still like to do things my way after a fact finding phase. I also make reference to TI and their design criteria for a choke in a switchmode buck regulator, which I think (hope) that we can agree that the switchmode buck topology is the closest model available to simulate the inverter function. I actually don't need agreement because I just needed a starting point that I could visualise to base a solution on and its the one I will use unless someone can demonstrate a better way. There are two formulas that TI use for Choke design that I will quote here: Formua 1. L = (Vout x (Vin - Vout)) divided by Delta(Iin) x fs x Vin Formula 2. Pinductor = I x I(Lrms) x R(Cu) + P(Core) which equates to I x I(IOut) x R(Cu) + P(Core) This all looks deceptively simple, BUT we don't have a fixed Vout or Iout, we have a 50Hz sinusoidal moving target and as we have a fixed frequency of ~ 20kHz. there are then a defined amount of steps each 50Hz cycle. So this is where the fun begins. We can't change the choke or frequency for the various levels that the "buck regulator" will use, the only "tools" we have is the inductor design and the duty cycle and whatever inductor we choose will be a compromise that has to be slanted to the highest power that we can envisage that the inductor will have to handle, as that is where the greatest power losses will occur. There are also some choice parameters for the choke material in the inductor that play a role. The Sendust material I keep on harping on about has characteristics that make it very suitable for the inverter's Power inductor, as the current through it increases, the previously calculated inductance reduces, which works in our favour for efficiency as we want more inductance at lower power levels but less at higher levels. If you refer to my previous post above, "choke design analysis pdf" & for Formula 1 (this post) above, plug in the values for 22.5 degrees V and delta(I) and at 90 degrees for V and Delta(I) the inductor values are 90 & 50uH I allowed 10uH extra (to be confirmed) for the toroid/Capacitor combination @ 20kHz, which makes the power inductor in the 40uH ballpark. To cater for switch on surges of equipment I try to over engineer/specify the inductor to a reasonable degree at max load of nominal steady state power, which allowing for the softer saturation characteristics gives a good margin against damaging saturation issues. If the inductor is too large then the ramping current will be too small to achieve enough storage energy it will also be physically large (and winding R will be higher than optimal) and if its too small there also wont be enough energy imparted to our choke due to insufficient ampere turns or insufficient energy storage volume. These are properties of inductive behaviour, not reactive behaviour. For anyone who is interested in more detail of Buck regulator or Inductor design here a few papers that you can refer to, No1 & 2 from Texas Instrument application and design. No 3 from NXP and I included No4 which is an 80 page Master Thesis document on Buck regulator design, from a Swedish University (written in English) with enough maths to drown anyone and where the word reactance is not mentioned even once (or in the other 3 documents I believe) - I am not the only one who does not consider or use reactance in certain fundamental switchmode applications. (maybe he was not granted his thesis.... I never looked it up) Doc 1 TI SMPS Buck_Basics_slva477b.pdf Doc 2 TI SMPS Choke Design slva057.pdf Doc 3 AN4716.pdf Doc 4 fulltext01.pdf I will close by saying that yes the Toroidal transformer, AC capacitor on the secondary and turns ratio are all part of an integrated design and have influences, but I propose to have a modestly overdesigned choke which will be a result of a few fundamental known design parameters fed into a formula and then if required at a later stage when we get some data feedback which may tweak the recipe for a better result if and as needed. New member -dex- re-found an earlier discovery here I had used previously about inductor design, which uses inputs of, Bsat (material saturation value for the core material), AL (core inductance factor), Ae value (cross sectional area) and the desired L, it then outputs Isat (saturation current) and Inductor Turns required. So for multiple stacked cores I found using Al (inductance factor) adding the Ae (cross section area) (multiplied by the number of cores used) it worked out quite accurately checked against the saturation tester. Warning - dont read his rant on core manufacturers...... Thanks for your input Rusty, we have arrived at quite similar ballpark values for the choke - albeit from different directions. The AC capacitor value is something to still factor in, 1 piece of the puzzle at a time. I don't buy much into the transformer natural resonance theory and huge runaway that Warp discussed here if the resonance of the toroid and capacitor occurred at 50Hz - I made a switched capacitor module for tuning at 50 & 75Hz and I reckon there was less distorion and phase shift at 50Hz. Edit: Just measured the leakage inductance of the Latronics 2kW/2.5kW ? toroidal that was already on the bench of ~ 6uH. My above guess of 10uH was not far off. This value stayed the same with a shorted output and for short removed and the AC Cap across the mains - but the rising current edge on the primary (unsurprisingly) grew some resonance ripples with the AC cap compared to the short Edited 2024-01-29 20:19 by wiseguy If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| poida Guru Joined: 02/02/2017 Location: AustraliaPosts: 1464 |

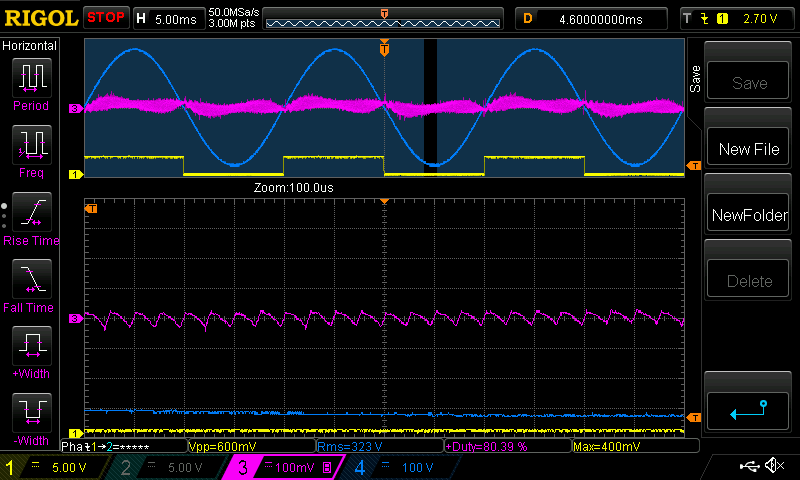

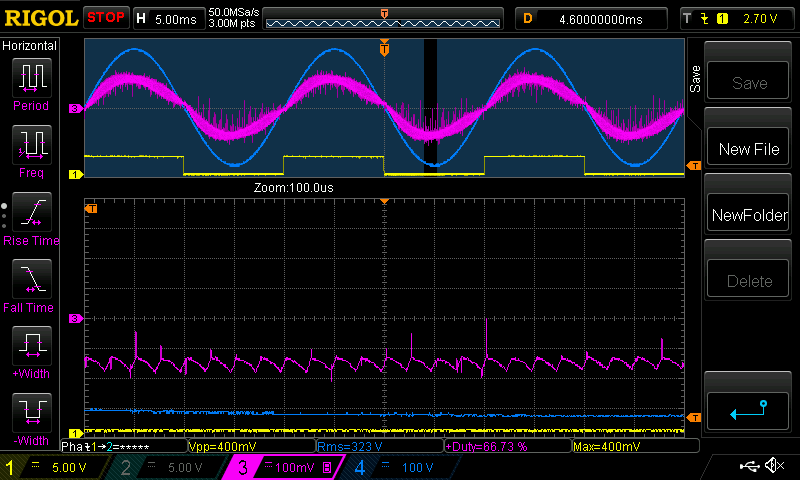

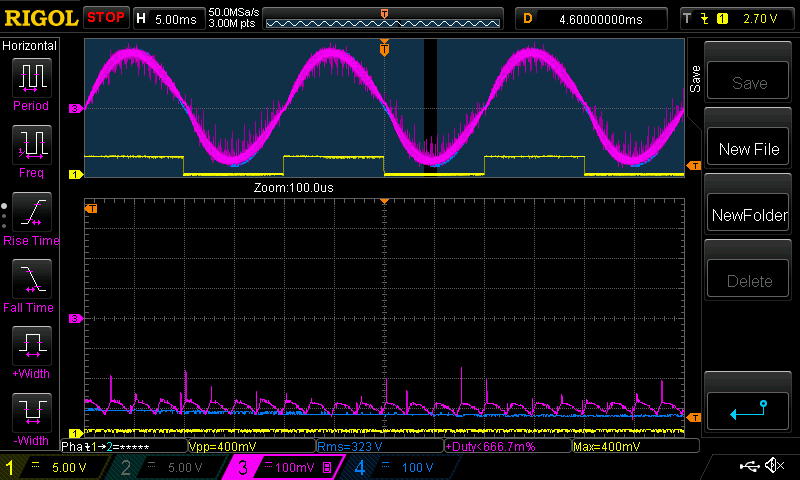

to see what is being put into the primary choke, all will be revealed with a current probe in series with the choke. You will see the "near DC" flowing through it, due to the AC load and the toroid reactance and you will also see the PWM on top of this much slower changing current. this is what I see with a current sensor in series with the choke and with no AC load. (what I call "idle")  and here it is with a load of about 100W  it seems to me that the current ripple in the choke does not change due to AC load, apart from a DC offset added to it. We might want to spend some time looking at the choke's inductance as a function of DC. Sure, it's not DC it's 50Hz AC. But for the 20 kHz PWM event, it may as well be DC. here it is with 200W load. more offset, but same ripple (close enough for me to call it the same)  Edited 2024-01-29 21:11 by poida wronger than a phone book full of wrong phone numbers |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Poida, not sure what loads you have applied there or what increase the next picture is or what the current scale is (ie 100mV = Amps?) or what inductance value we are looking at or what the turn ratio of the toroid or the input voltage applied so the next comments are next to useless probably. You don't need to plug in all those unknowns but I would be more interested in the actual choke value you chose and how you chose that value ? The p-p ripple will either have a fast rise leading edge and a longer slower fall - these are the delta I for the given choke. When looking at a fixed point of the waveform this is less evident as the difference in slope is a small adjustment for the dynamic losses as we load the Toroid (mostly R losses). As the load is increased for a well designed solution with more load the rising edge will be much longer and the falling edge will be faster but the P-P will not change a lot however if you look at the "hash" of the current waveform you can see the p-p level reduce a bit at the peak and quite a bit at the zero cross points. This variation of rise and fall slopes should be more obvious also as you move over the 50Hz waveform and check out the rise/fall of the sawtooth magnified at various points from 0 to 90 degrees and back again. The 50Hz Dc current is in the sine shape of the current waveform, more obvious with more load, the p-p is riding on the varying 50Hz dc as there is definitely more dc choke current with the rising 50Hz Dc level. You said "We might want to spend some time looking at the choke's inductance as a function of DC." I have mentioned that repeatedly that for the instantaneous currents this has the 50Hz DC current and whatever peak of the sawtooth inductor current which is certainly also related to the load - I do really like that 50Hz DC terminology as that is how I look at it in reality. OK I can see you edited since I posted and put a load value there - thanks. The choke must be able to cope with large varying 50Hz dc levels (the instantaneous peak A (not RMS) at full load) at the maximum inverter loads and still be able to retain some inductance properties. If you look at the graphs in the choke design pdf you can see the DC current values but remember these were all for the inverter fully loaded for that choke design at the 22.5, 45, 67.5, 90 degree points. Lastly I should mention that the waveforms at the 4 points are a slight fudge as they assume a fixed continuous output, but we all know that output is really changing sinusoidally so each current sawtooth inductor waveform is just a slight difference from the previous one, I think it was like 200 variations each complete 180 degrees Edited 2024-01-29 22:02 by wiseguy If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Poida did you add a third picture in the edit with the 200W or was it off my screen ? If it was there all along - sorry I missed it until after my reply post. I also missed the 100W load between the first 2 pictures which may have been there. I will take a break from this for a while I think and get more needed sleep ! If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| nickskethisniks Guru Joined: 17/10/2017 Location: BelgiumPosts: 472 |

Rustymotors, thanks for sharing, I see you derive 30uH based on filterdesign equations but then you need to know your capacitance as well, no? What did you use? While doing research a while ago I saw many people use this approach like here for example: https://electronics.stackexchange.com/questions/98300/50-60hz-inverter-output-inductor-design Mike, thanks for sharing the papers, what is Delta(Iin) ? Formua 1. L = (Vout x (Vin - Vout)) divided by Delta(Iin) x fs x Vin A while ago I came across this film, he has other video's too From the following youtube film, you can derive an alternative: https://www.youtube.com/watch?v=ZNUqGBBlKLI L = Vin / 4*fsw*Irms*1.41* (%ripple/100) But based on 6000W, 30% ripple, I have 7.4uH. With your 700W example it's like 63uH One of my many projects is building a hf inverter and I used the calculations out that persons videos with good results during experimentation/designing. To inspect your not entering the "danger zone" resonance, you can use those filter equations. I had another helpfull document about (Optimal inductor design and material selection for high power density inverters used in aircraft applications (hal.science)) But it's not accessible at this moment...  https://hal.science/hal-01532242/document What rustyrotors said about idle current was something I experienced to, there is probably a minimum inductance needed for lowest idle current. Although this was greatly influenced by the capacitor as well. Lastly a little less on topic (sorry) but what I found helpfull, we are all using big capacitors but what we exactly need also depends on the hf/50hz current ripple our inductor is influencing: https://www.ecicaps.com/tech-tools/technical-papers/selecting-film-bus-link-capacitors-high-performance-inverter-applications/ Edited 2024-01-30 07:34 by nickskethisniks |

||||

| poida Guru Joined: 02/02/2017 Location: AustraliaPosts: 1464 |

Mike, I first posted it with two images then re-read to check if I was making the point I wanted and added the 3rd image. I thought it was a great way to see what the choke is exposed to. To make it even clearer, we could add another trace, showing voltage across the choke, I would need to pull out the Tek Isolator for that. sorry to be again the source of confusion. wronger than a phone book full of wrong phone numbers |

||||

| rustyrotors Newbie Joined: 07/01/2023 Location: United StatesPosts: 36 |

yes, i used 2uF, which from experimentation resulted resonating with my transformer at roughly 90Hz, based on warpspeeds 1.5x recommendation. although honestly i do not understand how he came up with that suggestion. then multiply output capacitance by the sec/pri trans turn ratio squared to get primary capacitance, and use that for filter design. like warpspeed indicated, i have noticed if it resonates too close to 50/60Hz, my inverter will not start and makes terrible noises. above or below that its fine its interesting i have noticed too much choke inductance reduces high load efficiency too. when i went from a 2-stack sendust choke to a 4-stack, same number of turns, same wire length, idle dropped a watt or so, and when my fridge was running it gained 5-10W efficiency, but i lost about 100W efficiency up at 3+kW loads. it shows maybe a higher permeability core is optimum, so it loses some inductance at higher current. you want it to saturate for best efficiency, but maybe the downside is its harder on your FETs it for sure gets more complicated the further down the rabbit hole you go Edited 2024-01-30 09:05 by rustyrotors |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Ok lets take this one at a time. I am prepared to be like the saying "to a hammer everything looks like a nail". So my solution to use a normal buck regulator and their related equations model to solve the problem is maybe not the whole story, I am willing to accept that. Perhaps some of the other influences play a bigger part than expected. Please remember that I am still in theory land with my latest inverter. I don't want to kill it before I can extract as much useful info on the journey that I can, so I just wanted to get the choke right before the abuse - how hard can that be? Very hard it seems, my experimental loads up to 200W yields an efficiency around 95% when I remove the no load losses from the inverter idling. I asked for some input to a solution for the choke and presented my reasoning which was accepted with lets say less than enthusiasm, then I felt I had to explain/defend my reasoning. I am not trying to change anyone else perception in that process I was only trying to illustrate my reasoning. There are some inescapable fundamentals, I stand behind my analysis of the peak current from the source passing through the choke. My RMS to peak calculations have to be correct the energy comes from the source, no escaping that. The p-p ripple of the inductor that I added an extra 10% to cover the actual peak current of the 20kHz fundamental is the component that we/I will try to unravel. There is a p-p sawtooth across the inductor poidas images show us that so as that sawtooth has an average and therefore the peak choke current will be higher than the previously calculated 50Hz primary excited current, but by how much and how to calculate that ? Nick led me to an output inductor design page that also shows how difficult it is to get agreement on how to do this, one "helpful" fellow suggested that sendust is probably used for common mode chokes - er definitely not ! The part I liked is that an inductor of 370 odd microhenries was first calculated along with the use of a 10uF capacitor and then with a voila moment we shifted to 37uH and suggested an output capacitor of 60uF. It appears that the inverter in discussion is a HV inverter ie maybe 400V rail supply and no isolation transformer. The 780mA reactance at 50Hz with 10uF would be increased to nearly 5A of reactive idling current at no load which is close to 25% of the fully loaded inverter, so I'm not really onboard with this analysis and "solution" either. Is there a filter component to what the choke etc is doing, hell yeah no question, we don't want 20kHz on the mains output but maybe Nicks is right and a cookie cutter approach will get too hard to create. My approach was more to present a solution to create an inverter from scratch using readily available parts and with minimal risk of self destructing. I was hoping that the "model" would only alter slightly with regard to the power output required. I am going to wave a white flag here and return to the workbench and continue with my research into a suitable inductor which gives me reasonable idling and low load efficiency but not too much compromised losses at high loads either. When I have more data and information from this then I will try to find a design model that fits the results and present them for more fun discussions  Edited 2024-01-30 09:31 by wiseguy If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Nicks, Delta is the Greek symbol, usually presented as a triangle, its meaning is a difference or a change of a parameter. If you look at the TI pdfs the exact same formulas I wrote long hand in the post are presented in the pdf's in a much better normal mathematical expression. There is no easy way I have found to show maths expressions using this text editor for posting (we have a few symbols now but not enough). If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Rusty, what inverter are you using, is it an EG8010 or is it a Nano solution ? I have made both types of inverter and have not had any instability issues to date. My output capacitor experiments have all been in the 1uF to 4.7uF range, usually ending up with a value between 1 and 2.2uF. If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Nicks, "With your 700W example it's like 63uH". I think you missed the point here. I was plugging choke values for the 4 x 22.5 degree increments of load to show that the result is a bit of a compromise. The best results for the 4 points chosen all had different solutions with regard to the choke value that was the point I hoped to illustrate. If you want a 700W inverter 63uH may not be too far from the right value, but don't expect it to be the ideal choke for a 6kW output and be at optimum efficiency at full load. Is there a relationship between 700W & 63uH and 6000W and 7.4 uH - the number nine is coming into view..... maybe its just a crazy coincidence ? I looked at the you tube video too and I make the assumption of another 400V supply direct switching inverter. His design values ended up with 2 chokes around 4mH this is ~ 570 times larger than your inductor so please help me try to understand this discrepancy. I know we use 50VDC but I don't think that alone explains the discrepancy between the results. I am not confident that his is the correct approach for calculating our solution either given the topology that we use. Edited 2024-01-30 10:48 by wiseguy If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| phil99 Guru Joined: 11/02/2018 Location: AustraliaPosts: 3157 |

A partial answer is the reactance equation again. Using the original example of 50Hz, 20kHz PWM, 50V, 16µH XL at 20kHz is 5Ω so a very rough estimate of the peak current will be 50Vp-p / 5Ω ≈ 10Ap-p. The inductance of the primary will reduce that somewhat. I have used the peak voltage rather than the RMS as all the harmonics add a variable amount of current. The mix of harmonics vary as the mark / space ratio varies. At 50/50 there are only odd harmonics (60, 100kHz etc) with even harmonics (40, 80 etc) increasing either side of 50/50. Plus the inductance also varies somewhat with current. This current (as shown in Poida's scope shots) does not vary greatly (below saturation at least) as there is a fairly constant 50V p-p voltage (less the voltage drop across the primary inductance) across a fairly constant 5Ω. I guess this is more vague than you would like but there are so many variables. |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Ok Phil I am listening with new ears, I tried to ignore the circuitry beyond the 20kHz and the choke and treat it as a two terminal device for my calculations and using buck switching analysis. I know the load is a bit more complex as it has a mix of some small 20kHz content and a whole lot of 50Hz (slowly moving DC) component with some effects reflected back to the 20kHz and choke. So as I start to add higher powers through the choke I will try to work out how the 50Hz reactance and the 20kHz and the choke play together and what their relationship actually is. Edited 2024-01-30 11:45 by wiseguy If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| phil99 Guru Joined: 11/02/2018 Location: AustraliaPosts: 3157 |

I forgot to mention the reason there is about 50Vp-p across the choke is that the secondary side capacitor reflected in the primary has minimal impedance at 20kHz. @rustyrotors described this further up. |

||||

| rustyrotors Newbie Joined: 07/01/2023 Location: United StatesPosts: 36 |

eg8010, same here iirc it went crazy around 3uF, have not tried replicating it for obvious reasons  |

||||

| KeepIS Guru Joined: 13/10/2014 Location: AustraliaPosts: 2108 |

Wiseguys 8010 symmetry driver: Cap range tested 1uF to 12uF. I was specifically testing for the dreaded resonance we hear about, also monitoring AC harmonic distortion changes for each value and load condition using a HIOKI Power Quality Analyser. The cap made very little difference at all, harmonic distortion in this inverter is always dependent solely on the load quality, the same bad loads have the same results on mains power for obvious reasons. If your inverter is different - sorry. Each test ran for over an hour under all load conditions, no instability and no resonances in any part of the Inverter, no matter what value of cap I used. I settled on 3uF, for no other reason than it being a big high quality chassis mount, and happened to be close to the value usually supplied with the bigger 6kW to 10kW Chinese boards, seems to be their "one size fits all" for any transformer used - those carfty Chinese. . NANO:Inverter V 8.2ks - Linux AvrDude GUI script V4.1 |

||||

| phil99 Guru Joined: 11/02/2018 Location: AustraliaPosts: 3157 |

I can imagine some inverters may be fussy about the capacitor size at no load if the feedback has a slow response to resonance. However at 240V 50Hz a 3.5µF cap draws ¼A, 13.5µF = 1A. This is swamped once you switch anything much on. It's main function is to work with the inductor to filter the PWM. |

||||

| KeepIS Guru Joined: 13/10/2014 Location: AustraliaPosts: 2108 |

Yes, I found this in testing, which is why I gave up some filtering of PWM with the choke value and the cap value. I personally think that strange behavior is indicative of an underlining problem or design difference causing any slight weakness to appear and amplify under certian load line conditions. My main point was that destructive resonances around 50Hz do NOT happen - In my inverter. The 3uF cap resonates the toriod around 50Hz, sometimes, or 70Hz or 40Hz or 105Hz depending on the magnetic state of the core. Anyway, I think this is getting slightly off topic, so apology to Mike. . NANO:Inverter V 8.2ks - Linux AvrDude GUI script V4.1 |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Input like this is not off topic - all relevant in making a happy stable inverter. You can see how in one instance the cap value makes it unstable but for another using a slight design difference it appears unconditionally stable. In our iteration of the EG8010 there is minimal delay as we feed back an AC reference from the transformer to the EG8010 and it seems to work a treat. In every one of their (EG Micro the 8010 guys ) designs except their version of a 48V transformer inverter they do the same. But for the 48V one they rectify and use a 4u7 (around a 1 second delay compared to ~ 20mS for all the others), and a lot of EG8010 builds have had issues maybe a coincidence hmmm... If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| The Back Shed's forum code is written, and hosted, in Australia. | © JAQ Software 2026 |