# **Buck Converter Design Issues**

Master thesis performed in *division of Electronic Devices* by

# Muhammad Saad Rahman

Thesis No: LiTH-ISY-EX--06/3854--SE Linköping Date: 2007-07-17

# **Buck Converter Design Issues**

Master thesis in Electronic Devices at

Linköping Institute of Technology by

Muhammad Saad Rahman LiTH-ISY-EX--06/3854--E

**Examiner/Supervisor**: Prof. Dr. Atila Alvandpour **Co-Supervisor**: Lic. Henrik Fredriksson

Linköping 2007-07-17

| Presentation date:<br>2007-5-28<br>Publication date: | Division of Electronic Devices<br>Department of Electrical Engg. | Linköpings universitet          |

|------------------------------------------------------|------------------------------------------------------------------|---------------------------------|

| Language                                             | Type of Publication                                              | ISBN (Licentiate thesis)        |

| •English Swedish                                     | Licentiate thesis  Degree thesis Thesis C-level                  | ISRN:<br>LiTH-ISY-EX06/3854SE   |

| 103 Thesis D-level Report                            | Thesis D-level                                                   | Title of series (Master thesis) |

|                                                      | Other (specify below)                                            | Series number/ISSN ()           |

URL, Electronic Version <a href="http://www.ep.liu.se">http://www.ep.liu.se</a>

Publication Title

Buck Converter Design Issues

Author

Muhammad Saad Rahman

#### **Abstract**

Switch Mode Power Supplies are very important components in present day electronics and have continued to thrive and grow over the past 25 years. This thesis looks inside how the SMPS have evolved over the passage of years with special emphasis to the Synchronous Buck Converter. It also discusses why there is a strong potential to further the study related to designs based around a Synchronous Buck Converter for portable applications. The main objective of the thesis is to look into the controller design for minimizing size, enhancing efficiency and reliability of power converters in portable electronic equipment such as mobile phones and PDAs. The thesis aims to achieve this using a 90 nm process with an input voltage of 1.55V and an output of 1V with a power dissipation of 200 mW.

Key Words: Switch Mode Power Supplies, Buck Converter, Voltage Mode Control, Compensator

# **Team Involved**

# Prof. Dr. Atila Alvandpour Examiner/Supervisor

Division of Electronics Devices

Department of Electrical Engineering

Linköping University

SE-581 83 Linköping, Sweden

Phone: +46 (0)13-285818

Mobile: +46 (0)708-485818 Fax: +46 (0)13-139282 Email: atila@isy.liu.se

### Henrik Fredriksson PhD Student Lic., M.Sc.EE Co-Supervisor

Division of Electronics Devices

Department of Electrical Engineering

Linköping University

Office phone: +46(0)13 282254

Fax: +46(0)13 139282 E-mail: henfr@isy.liu.se

# Muhammad Saad Rahman Student M.Sc. EE (Socware)

Mobile: +46(0)73 5690667 Fax: +46(0)13 139282 E-mail: muhra223@student.liu.se msaadrahman@yahoo.com

# Abbreviations

| BJT                                       | Bipolar Junction Transistor                       |  |  |

|-------------------------------------------|---------------------------------------------------|--|--|

| CCM                                       | Continuous Conduction Mode                        |  |  |

| CMC                                       | Current Mode Control Complementary MOS            |  |  |

| CMOS                                      |                                                   |  |  |

| DC                                        | Direct Current                                    |  |  |

| DCM                                       | Discontinuous Conduction Mode                     |  |  |

| DCR                                       | Direct Current Resistance                         |  |  |

| ESL                                       | Equivalent Series Inductance                      |  |  |

| ESR                                       | Equivalent Series Resistance                      |  |  |

| MOSFET                                    | Metal Oxide Semiconductor Field Effect Transistor |  |  |

| NFET                                      | Negative Channel Field Effect Transistor          |  |  |

| PDA                                       | Personal Digital Assistants                       |  |  |

| PFM                                       | Pulse Frequency Modulation                        |  |  |

| PWM                                       | Pulse Width Modulation                            |  |  |

| SMPS Switch Mode Power Supplies           |                                                   |  |  |

| SRBC Synchronous Rectifier Buck Converter |                                                   |  |  |

| VLSI Very Large Scale Integration         |                                                   |  |  |

| VMC                                       | Voltage Mode Control                              |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

|                                           |                                                   |  |  |

### **Abstract**

Switch Mode Power Supplies (SMPS) are very important components in present day electronics and have continued to thrive and grow over the past 25 years. This thesis looks inside how the SMPS have evolved with special emphasis to the Synchronous Rectifier Buck Converter (SRBC). It also discusses why there is a strong potential to further the study related to designs based around a SRBC for portable applications. The main objective of the thesis is to look into the controller design for minimizing size, enhancing efficiency and reliability of power converters in portable electronic equipment such as mobile phones and PDAs. The thesis aims to achieve this using a 90nm process with an input voltage of 1.55V and an output of 1V with a power dissipation of approximately 200mW.

### **Preface**

This master thesis is related to the design of a Buck Converter. Prof. Dr. Atila Alvandpour is the thesis examiner/supervisor and Lic. Henrik Fredriksson is the co-supervisor of my thesis work. Master thesis consists of 20 Swedish point's equivalent to 30 ECTS points.

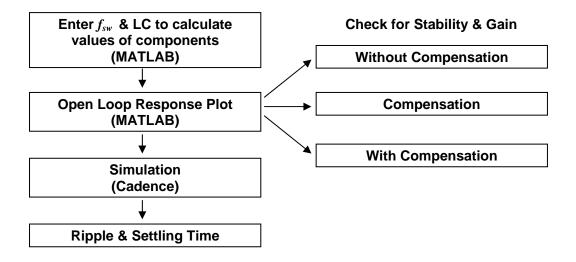

The scope of thesis work includes the study of a Buck Converter and the issues involved in designing a Buck Converter. How a Buck Converter works with different types of isolation, the different kinds of modes available in Buck Converter, the Mode for which it has to be designed (Current Control / Voltage Mode), the design of the controller and the most important part of the designing of the Compensator. The system level study has been conducted using MATLAB and then simulated using the 90nm library.

Chapter 1 introduces the issues involved in power supplies. It also looks at why SMPS are preferred and concludes with a comparison between the Linear and Switch Mode Regulators.

Chapter 2 describes what SMPS are and what their current applications are. Also it briefly explains the different type of converters available.

Chapter 3 throws light on the actual Buck Converter and the theory of operation of the Buck Converter. The topics covered are how we reach to the SRBC which is used in this thesis. It also discusses the different mode – Continuous and the Discontinuous mode.

Chapter 4 deals with the Control of the Buck Converter. It discusses the PWM and the different techniques used in the control such as the Voltage Mode Control and the Current Mode Control.

Chapter 5 deals with the step by step designing of the Buck Converter and its subsequent controller based on the requirements of a 1.55V input and a 1 V output with 200mW output power. The chapter proceeds in a step by step manner in designing a Buck Converter.

Chapter 6 covers all the references that have been consulted for the preparation of this thesis report.

Dedicated to Mummy and Abbi, who have always supported me in all my endeavours .....

### **Acknowledgments**

First of all I am thankful to Almighty Allah who has provided me the strength to successfully complete my Masters Thesis. Though their have been so many people who have played a role for my successful completion of my Masters Degree but to mention a few who have played a very major role:

Prof. Dr. Atila Alvandpour, who introduced me to the field of Power Electronics and provided me guidance and vision in my work..

Henrik Fredriksson, my co-supervisor, who very patiently solved my problems. I shall always strive for the *engineering* approach that he used to profess - to gather that feel for things.

Prof. Dr. Michael A. E. Andersen of the Power Electronics Group at DTU for his comments on my work and renewed guidance in the field of power electronics.

Rashad Ramzan *Sb* whose being around helped so much. Apart from the technical discussions, his company and advice in other matters was very helpful. I can contribute much of my remaining sanity (and insanity) to him.

Martin Hansson, Timmy Sundstrom & Naveed Ahsan for their help in matters. Especially to ever helpful Martin who would go out of his way to explain things in a better way.

Arta Alvandpour & Anna Folkeson for the administrative support.

Azam Akbar & Nasir Mehmood, my room mates in the early days. Azam's light hearted attitude really helped to get away from the daily tensions during the course work and Nasir's approach towards his studies created a source of inspiration for me and helped me strive harder.

Our friends from SoC 2005: Ahmed Sher, Amir Eghbali, Amjad Altaf, Asad Abbas, Ghulam Mehdi, Hassan Raza, Lim Boon Shuang, Mahesh Balaji, Vinod Ravinath, Yi Hsei Li who have been very kind and helpful.

Dr. Qamar Wahab and Mufti Sb who made Summer 2006 a truly enjoyable and remember able experience.

Ahsanullah Kashif & Sher Azam Sb who introduced the bi-weekly group discussion and dinner. The resulting discussions at those get-togethers really helped me grow and broaden my vision of things outside the domain of my studies.

Muhammad Asif & Asad Ali the "Company" which was very understanding towards the final stages of my thesis work and also all the other residents of 12A: Ghassan Bhatti, Muhammad Tanveer, Waqar-ul-Hasan & Taimur Shahzad.

Dr. Umer, Malik Ali Shahid, Asad Naeem, Farrukh Zaman, Saqib Mehmood & Farhan Gul who had added inspiration during my studies and encouraged me for pursuing my MSc.EE from Sweden.

Rizwan Masood & Humayun Ejaz who stayed in touch me with and helped me sort out a lot of issues back home during my stay in Sweden.

Mahnoor, my niece, whose continued persistence of when I would return to Pakistan made me work a *little faster* on my thesis.

Farheen, my *fru*, who supported and helped me during her stay in Sweden with me and also afterwards when she went back to Pakistan.

Salman Rahman, my elder brother who introduced me to Linkoping University and provided me guidance with the Swedish ways.

Samia Hasan & Saeed-ul-Hassan, my sister and brother-in-law who supported me in my endeavours and tried to figure out better opportunities for me.

Seema Rahman & Shahzad Khalil, my younger sister and brother-in-law, who aptly took care of things back home (which I could not have taken care of during my stay in Sweden) and let me focus on my studies.

Shamim-ur-Rahman & Shahnaz Rahman, my parents who since my childhood have had to face so many problems in my up bringing. They are truly worth many gold medals for raising me for as far as I have come. Had it not been their support and guidance at every step, my educational journey would have ended a long time back.

# **Table of Contents**

| List of Figures                                           | xxi   |

|-----------------------------------------------------------|-------|

| List of Tables                                            | xxiii |

| 1. Introduction                                           | 1     |

| 1.2 Why use a switching regulator?                        | 2     |

| 2. DC-DC Converter                                        | 7     |

| 2.1 Introduction                                          | 7     |

| 2.2 What are SMPS?                                        | 7     |

| 2.3 Types of Converters                                   | 8     |

| 2.3.1 Non-Isolated DC/DC Converters                       | 8     |

| 2.3.2 Isolated DC/DC Converters                           | 8     |

| 2.4 Why work on Buck Converters?                          | 9     |

| 3. Buck Converter – Theory of Operation                   | 11    |

| 3.1 Evolution of a Buck Converter                         | 11    |

| 3.2 Purpose of different components in the Buck Converter | ·14   |

| 3.2.1 Switch                                              | 14    |

| Operating Frequency                                       | 15    |

| 3.2.2 Inductor                                            | 16    |

| 3.2.3 Capacitor                                           | 17    |

| 3.2.4 Freewheeling Diode/Transistor                       | 17    |

| 3.2.5 Feedback                                            | 18    |

| 3.3 States of Operation                                   | 18    |

| 3.3.1 ON State                                            | 19    |

| 3.3.2 OFF State                                           |       |

| 3.3.3 Continuous Mode / Discontinuous Mode                | 20    |

| 3.4 Synchronous Buck Converters                           | 21    |

| 3.4.1 Introduction                                        | 21    |

| 3.4.2 Topology                                            | 21    |

| 3.4.3 Improvements                                        | 22    |

| 3.4.4 Problems                                            | 22    |

| 4. Practical Issues of Buck Converter                     |       |

| 4.1 Calculation for Duty Ratio                            | 25    |

| 4.2 Calculation for Inductor                              | 26    |

| 4.3 Calculation for Capacitor                             | 30    |

| 4.4 PWM Controller                                        | 31    |

| 4.4.1 PWM                                                 |       |

| 4.4.2 Comparator and Voltage to PWM Converter             |       |

| 4.5 Feedback Control System                               | 33    |

| 4.6 Linearization using State-Space Averaging             | 35    |

| 4.6.1 Power Stage & Output Filter                         |       |

|    | Buck Converter                                      | 38 |

|----|-----------------------------------------------------|----|

|    | 4.6.2 Pulse Width Modulator                         | 42 |

|    | 4.7 Stability Criteria                              | 43 |

|    | 4.8 Compensator                                     |    |

|    | 4.8.1 Type I Compensation                           | 46 |

|    | 4.8.2 Type II Compensation                          |    |

|    | 4.8.3 Type III Compensation                         |    |

|    | 4.9 Feed Forward                                    |    |

|    | 4.10 Voltage Mode Control / Current Mode Control    | 52 |

|    | 4.10.1 Voltage Mode Control                         |    |

|    | 4.10.2 Current Mode Control                         | 54 |

|    | 4.11 TradeOffs for Implementation of CMC & VMC      | 55 |

| 5. | . Designing a practical Buck Converter              |    |

|    | 5.1 Design Equations                                |    |

|    | 5.2 Input Parameters                                | 58 |

|    | 5.3 Buck Converter Circuit.                         | 58 |

|    | 5.4 Calculating Parameters                          | 59 |

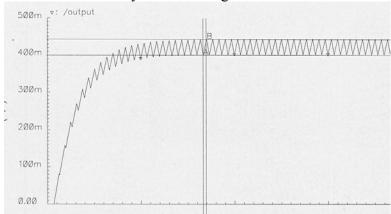

|    | 5.5 Evaluation                                      | 62 |

|    | 5.5.1 Maximum Load                                  | 62 |

|    | 5.5.2 Load Switching                                | 62 |

|    | 5.5.3 Power Efficiency                              | 63 |

|    | 5.5.4 Chip Area                                     | 63 |

|    | 5.5.4.1 Capacitor                                   | 64 |

|    | 5.5.4.2 Resistor                                    | 64 |

|    | 5.9 Conclusion                                      | 64 |

|    | 5.10 Future Work                                    | 65 |

| 6. | . References                                        | 67 |

|    | Books                                               | 67 |

|    | Papers                                              | 67 |

|    | Websites                                            | 68 |

| A  | ppendix                                             | 71 |

|    | Appendix A – Values of L&C                          |    |

|    | Appendix B - Open Loop & Closed Loop                | 72 |

|    | Appendix C - Steady-State Operation                 | 73 |

|    | Appendix D – MATLAB Code                            | 74 |

|    | Appendix E - Computer Simulation Process & Problems | 76 |

|    | Appendix F - Linear Differential Equations          |    |

|    | Appendix G - Development Work Flow                  | 79 |

|    |                                                     |    |

# List of Figures

| Figure 1: Interdisciplinary nature of Power Electronics [1]                               | 1    |

|-------------------------------------------------------------------------------------------|------|

| Figure 2: Power Supply Tree [27]                                                          | 2    |

| Figure 3: Linear Regulator                                                                |      |

| Figure 4: Switching Regulator                                                             |      |

| Figure 5: Block Diagram of a Switch Mode Power Supply [1]                                 | 8    |

| Figure 6: Buck regulators in the system [35]                                              |      |

| Figure 7: Complete Switching Regulator Topology                                           | 11   |

| Figure 9: Effect of an Inductor                                                           |      |

| Figure 10: Circuit with an LC Filter                                                      |      |

| Figure 11: Buck Converter with load resistor                                              |      |

| Figure 12: Step Down Switch Mode Power Supply                                             | 14   |

| Figure 13: General Buck Converter Schematic                                               |      |

| Figure 14: ON State                                                                       |      |

| Figure 15: OFF State                                                                      | 19   |

| Figure 16: (a) Continuous Mode (b) Discontinuous Mode                                     | 20   |

| Figure 17: Complementary switches                                                         | 21   |

| Figure 18: Step-down converter circuit states (assuming i <sub>L</sub> flows continuously | y):  |

| (a) switch on; (b) switch off [1]                                                         | 25   |

| Figure 19: Inductor Current                                                               |      |

| Figure 20: The source current                                                             | 28   |

| Figure 21: Current through the low side MOSFET                                            | 29   |

| Figure 22: Output voltage ripple in a step-down converter                                 |      |

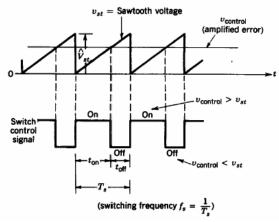

| Figure 23: PWM Signal                                                                     | 32   |

| Figure 24: Voltage Reference Comparator [1]                                               | 32   |

| Figure 25: PWM Comparator Signals                                                         |      |

| Figure 26: Feedback Control System                                                        | 34   |

| Figure 27: Linearized Feedback Control System                                             | 35   |

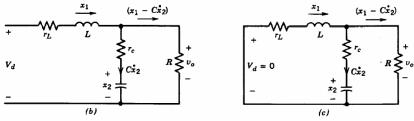

| Figure 28: Buck Converter Circuit [1]                                                     | 38   |

| Figure 29: Buck Converter (a) switch on; (b) switch off                                   | 38   |

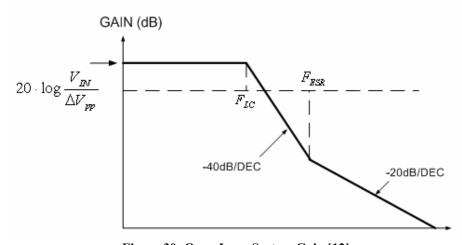

| Figure 30: Open Loop System Gain [12]                                                     | 41   |

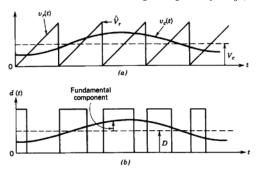

| Figure 31: Pulse-width modulator                                                          | 42   |

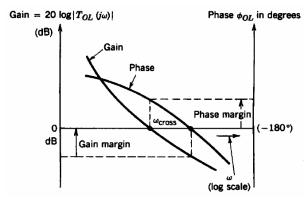

| Figure 32: Definitions of the crossover frequency, phase and gain margins                 | 45   |

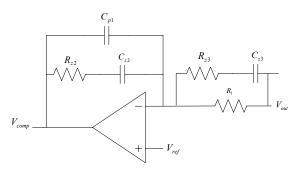

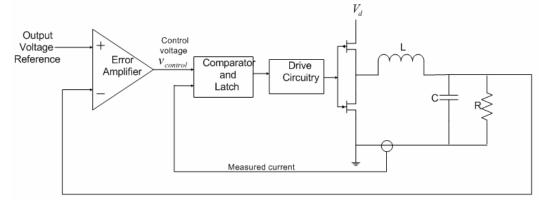

| Figure 33: A general compensated error amplifier                                          | 45   |

| Figure 34: Type I Compensation [13]                                                       | 46   |

| Figure 35: Type II Compensation                                                           |      |

| Figure 36: Generic Type II Network                                                        |      |

| Figure 37: Type III Compensation                                                          | 50   |

| Figure 38: Generic Type III Network                                                       | . 50 |

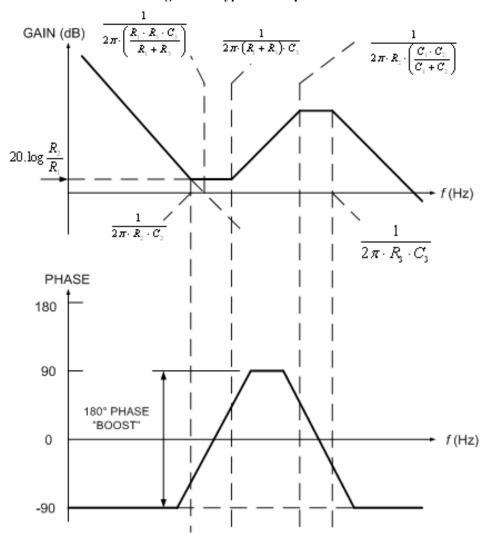

| Figure 39: PWM Duty Ratio Control   1                  | 53 |

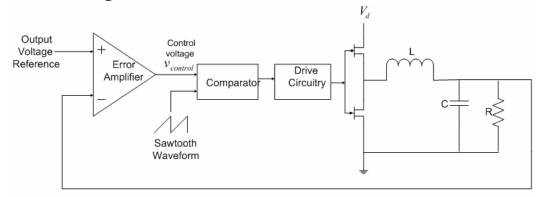

|--------------------------------------------------------|----|

| Figure 40: Current Mode Control [1]                    | 54 |

| Figure 41: Buck Converter Circuit                      | 58 |

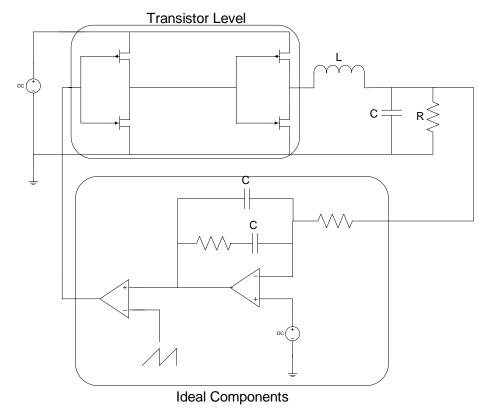

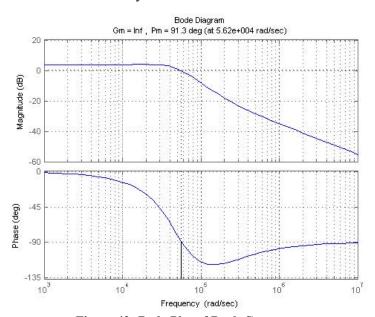

| Figure 42: Bode Plot of Buck Converter                 | 59 |

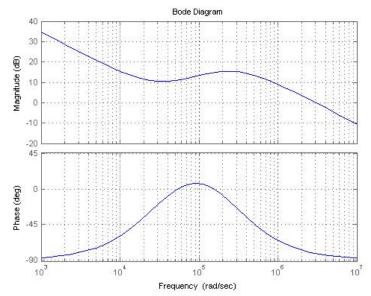

| Figure 43: Bode Plot of Type III Compensation Network  | 60 |

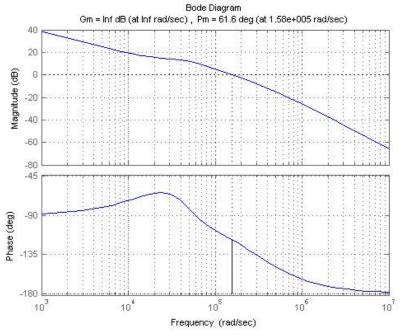

| Figure 44: Bode Plot of Total Open Loop Buck Converter | 60 |

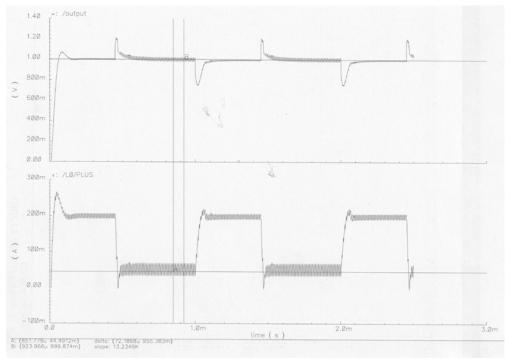

| Figure 45: Load Switching from $5\Omega$ to $19\Omega$ | 63 |

| Appendix Figure 1: Feedback Loop                       | 72 |

| Appendix Figure 2: Unstable Current                    | 73 |

| Appendix Figure 3: Decaying Current                    | 73 |

| Appendix Figure 4: Steady-State Current                | 73 |

| Appendix Figure 5: Measuring Ripple                    | 76 |

| Appendix Figure 6: Buck Converter                      | 77 |

|                                                        |    |

# List of Tables

| Table 1: Comparison between Linear and Switch-Mode Regulators [17]       | 5  |

|--------------------------------------------------------------------------|----|

| Table 2: Voltage Mode vs Current Mode Control [22]                       | 54 |

| Table 3: Buck Converter Specifications                                   | 57 |

| Table 4: Calculated Parameters                                           | 59 |

| Table 5: Results                                                         | 61 |

| Table 6: For $R_L = 5\Omega$ , ESR = DCR = 1, $R_1 = 60 \text{ k}\Omega$ | 61 |

| Table 7: $R_L = 19Ω$ , $ESR = DCR = 1$ , $R_1 = 60kΩ$                    | 61 |

| Table 8: ESR=30E-3, DCR=1, $R_1$ =60k $\Omega$                           | 62 |

| Table 9: Maximum Load Conditions                                         | 62 |

### 1. Introduction

Over the years as the portable electronics industry progressed, different requirements evolved such as increased battery lifetime, small and cheap systems, brighter, full-colour displays and a demand for increased talk-time in cellular phones. An ever increasing demand from power systems has placed power consumption at a premium. To keep up with these demands engineers have worked towards developing efficient conversion techniques and also has resulted in the subsequent formal growth of an interdisciplinary field of Power Electronics. However it comes as no surprise that this new field has offered challenges owing to the unique combination of three major disciplines of electrical engineering: electronics, power and control [3].

Figure 1: Interdisciplinary nature of Power Electronics [1]

These multi-discipline technologies, as highlighted in Figure 1-1, have involved control theory, filter synthesis, signal processing, thermal control, and magnetic components design [8].

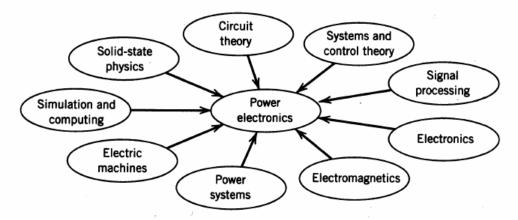

This thesis looks at the design issues associated with designing dc/dc converters (Figure 1-2).

Figure 2: Power Supply Tree [27]

# 1.2 Why use a switching regulator?

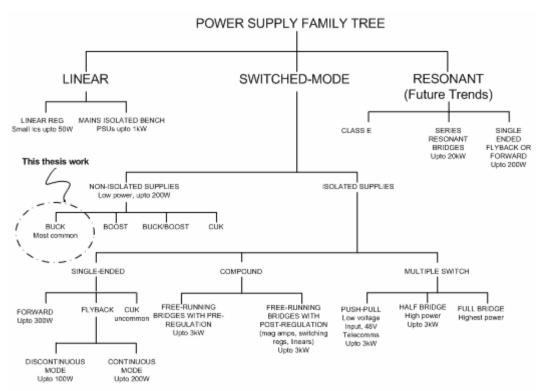

Voltage regulation conventionally has been done by Linear Regulators but slowly is being replaced with Switching Regulators. To realize the importance of a switching regulator we will first compare its efficiency with a linear regulator. The resistance of the linear regulator varies in accordance with the load resulting in a constant output voltage [16].

Figure 3: Linear Regulator

Figure 1-3 shows a simple Linear Regulator. If we consider an example, where  $V_{in} = 24$  and we want to have a  $V_{out} = 12$ . In this case we need to drop 12 volts across the regulator.

Using standard power equation:

$$P = I \cdot V \tag{Eq. 1-1}$$

If the output current = 10A, this will result in 10 A \* 12 V = 120 W.

Now the regulator must dissipate 120 W of heat energy. This results in a mere 50% efficiency for the linear regulator and a lot of wasted power which is normally transformed into heat. Provision for heat sinks for cooling makes the regulator bulky and large. Hence, where size and efficiency are critical, linear voltage regulators cannot be used.

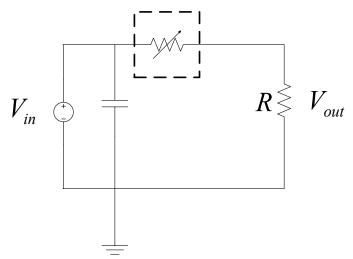

Figure 1-4 is a very basic switching regulator. The switching regulator is a simple switch (and hence ideally no resistance or very low resistance). This switch goes on and off at a fixed rate (usually between 50 KHz to 100 KHz) as shown in Figure 1-4.

Figure 4: Switching Regulator

The Duty Cycle for the switch is determined by the Eq. 1-2.

Duty

$$Cycle = \frac{V_{out}}{V_{in}}$$

(Eq. 1-2)

The time that the switch remains closed during each switch cycle is varied to maintain a constant output voltage. The switching regulator is much more efficient than the linear regulator achieving efficiencies as high as 80% to 95% in some circuits. In contrast, the linear regulator usually exhibits only 50% to 60% efficiency. With higher efficiency smaller heat sinks will be required because lesser heat is dissipated. This further results in SMPS, that can be packaged in a fraction of the size of linear regulators.

There is also another advantage of Switching Regulators and that is that the energy stored by inductor & capacitor can be transformed to output voltages that can be greater than input (boost), negative (inverter), or can be transferred through a transformer to provide electrical isolation with respect to the input.

Unlike linear regulators, switched power supplies can step up or step down the input voltage [14].

All of our discussion can be summarized with a comparison in Table 1:

|                   | Linear                                                                                                                                                        | Switching                                                                                                                                        |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Function          | Only steps down; input voltage must be greater than output.                                                                                                   | Steps up, steps down, or inverts                                                                                                                 |

| Efficiency        | Low to medium, but actual battery life depends on load current and battery voltage over time; high if $V_{\text{IN}}$ - $V_{\text{OUT}}$ difference is small. | <b>High</b> , except at very low load currents $(\mu A)$ , where switch-mode quiescent current is usually higher.                                |

| Waste Heat        | <b>High,</b> if average load and/or input/output voltage difference are high                                                                                  | Low, as components usually run cool for power levels below 10W                                                                                   |

| Complexity        | <b>Low,</b> which usually requires only the regulator and low-value bypass capacitors                                                                         | Medium to high, which usually requires inductor, diode, and filter caps in addition to the IC; for high-power circuits, external FETs are needed |

| Size              | Small to medium in portable designs, but may be larger if heat sinking is needed                                                                              | Larger than linear at low power, but<br>smaller at power levels for which<br>linear requires a heat sink                                         |

| <b>Total Cost</b> | Low                                                                                                                                                           | Medium to high, largely due to external components                                                                                               |

| Ripple/Noise      | <b>Low</b> ; no ripple, low noise, better noise rejection.                                                                                                    | <b>Medium to high</b> , due to ripple at switching rate                                                                                          |

Table 1: Comparison between Linear and Switch-Mode Regulators [17]

### 2. DC-DC Converter

#### 2.1 Introduction

DC-DC converters are electronic devices that are used whenever we want to change DC electrical power efficiently from one voltage level to another. In the previous chapter we mentioned the drawbacks of doing this with a linear regulator and presented the case for SMPS. Generically speaking the use of a switch or switches for the purpose of power conversion can be regarded as a SMPS. From now onwards when ever we mention DC-DC Converters we shall address them with respect to SMPS.

A few applications of interest of DC-DC converters are where 5V DC on a personal computer motherboard must be stepped down to 3V, 2V or less for one of the latest CPU chips; where 1.5V from a single cell must be stepped up to 5V or more, to operate electronic circuitry. In all of these applications, we want to change the DC energy from one voltage level to another, while wasting as little as possible in the process. In other words, we want to perform the conversion with the highest possible efficiency.

DC-DC Converters are needed because unlike AC, DC can't simply be stepped up or down using a transformer. In many ways, a DC-DC converter is the DC equivalent of a transformer. They essentially just change the input energy into a different impedance level. So whatever the output voltage level, the output power all comes from the input; there's no energy manufactured inside the converter. Quite the contrary, in fact some is inevitably used up by the converter circuitry and components, in doing their job.

### 2.2 What are SMPS?

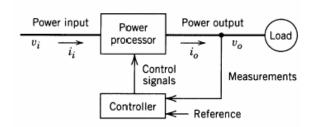

High frequency switching converters are power circuits in which the semiconductor devices switch at a rate that is *fast compared to the variation of the input and output waveforms*. Figure 2-1 shows a generic block diagram of a SMPS. The difference between the switching frequency and the frequency of the external waveforms is large enough to permit the use of low-pass filters to remove the unwanted switching frequency components. High frequency switching converters are used most often as interfaces between dc systems of different voltage levels. These converters are known as *high-frequency dc/dc converters*, and examples of their use are the power supplies in computers and other electronic equipment. High frequency switching converters can also be

Figure 5: Block Diagram of a Switch Mode Power Supply [1]

used as an interface between dc and ac systems [18].

### 2.3 Types of Converters

Currently, dc/dc converters can be divided into two broad categories:

- Non-isolated dc/dc converters

- Isolated dc/dc converters

### 2.3.1 Non-Isolated DC/DC Converters

The non-isolated converter usually employs an inductor, and there is no do voltage isolation between the input and the output. The vast majority of applications do not require do isolation between input and output voltages. The non-isolated do-do converter has a do path between its input and output.

Battery-based systems that don't use the ac power line represent a major application for non-isolated dc-dc converters. Point-of-load dc-dc converters that draw input power from an isolated dc-dc converter, such as a bus converter, represent another widely used non-isolated application.

Most of these dc-dc converter ICs use either an internal or external synchronous rectifier. Their only magnetic component is usually an output inductor and thus less susceptible to generating electromagnetic interference. For the same power and voltage levels, it usually has lower cost and fewer components while requiring less pc-board area than an isolated dc-dc converter. For lower voltages (12V) non-isolated buck converters can be used.

### 2.3.2 Isolated DC/DC Converters

For safety considerations, there must be isolation between an electronic system's ac input and dc output. Isolation requirements cover all systems operating from the ac power line, which can include an isolated front-end ac-dc power supply

followed by an isolated "brick" dc-dc converter, followed by a non-isolated point-of-load converter. Typical isolation voltages for ac-dc and dc-dc power supplies run from 1500 to 4000V, depending on the application. An isolated converter employs a transformer to provide dc isolation between the input and output voltage which eliminates the dc path between the two.

Isolated dc-dc converters use a switching transformer whose secondary is either diode-or synchronous-rectified to produce a dc output voltage using an inductor-capacitor output filter. This configuration has the advantage of producing multiple output voltages by adding secondary transformer windings. For higher input voltages (48V) transformer isolated converters are more viable [19].

### 2.4 Why work on Buck Converters?

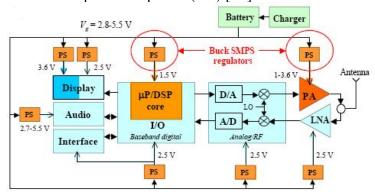

The buck converter is the most widely used dc-dc converter topology in power management and microprocessor voltage-regulator (VRM) applications. Those applications require fast load and line transient responses and high efficiency over a wide load current range. They can convert a voltage source into a lower regulated voltage. For example, within a computer system, voltage needs to be stepped down and a lower voltage needs to be maintained. For this purpose the Buck Converter can be used [20]. Furthermore buck converters provide longer battery life for mobile systems that spend most of their time in "stand-by". Buck regulators are often used as switch-mode power supplies for baseband digital core and the RF power amplifier (PA) [35].

Figure 6: Buck regulators in the system [35]

# 3. Buck Converter – Theory of Operation

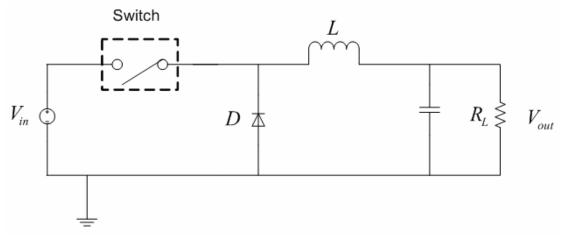

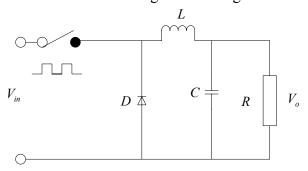

The name "Buck Converter" presumably evolves from the fact that the input voltage is bucked/chopped or attenuated, in amplitude and a lower amplitude voltage appears at the output. A buck converter, or step-down voltage regulator, provides non-isolated, switch-mode dc-dc conversion with the advantages of simplicity and low cost. Figure 7 shows a simplified non-isolated buck converter that accepts a dc input and uses pulse-width modulation (PWM) of switching frequency to control the output of an internal power MOSFET. An external diode, together with external inductor and output capacitor, produces the regulated dc output.

Buck, or step down converters produce an average output voltage lower than the input source voltage.

Figure 7: Complete Switching Regulator Topology

### 3.1 Evolution of a Buck Converter

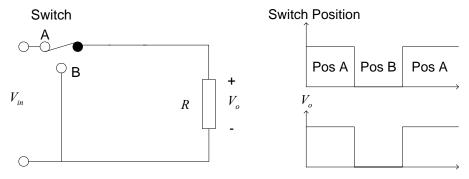

The buck converter here onwards is introduced using the evolutionary approach. Let us consider the circuit in Figure 8, containing a single pole double-throw switch.

Figure 8: A resistor with a single-pole double-throw switch

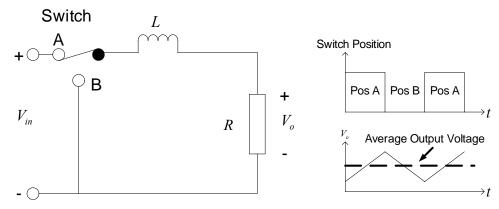

For the circuit in Figure 8, the output voltage equals the input voltage when the switch is in position A and it is zero when the switch is in position B. By varying the duration for which the switch is in position A and B, it can be seen that the average output voltage can be varied, but the output voltage is not pure dc. The circuit in Figure 8 can be modified as shown in Figure 9 by adding an inductor in series with the load resistor. An inductor reduces ripple in current passing through it and the output voltage would contain less ripple content since the current through the load resistor is the same as that of the inductor. When the switch is in position A, the current through the inductor increases and the energy stored in the inductor increases. When the switch is in position B, the inductor acts as a source and maintains the current through the load resistor. During this period, the energy stored in the inductor decreases and its current falls. It is important to note that there is continuous conduction through the load for this circuit. If the time constant due to the inductor and load resistor is relatively large compared with the period for which the switch is in position A or B, then the rise and fall of current through inductor is more or less linear, as shown in Figure 9.

Figure 9: Effect of an Inductor

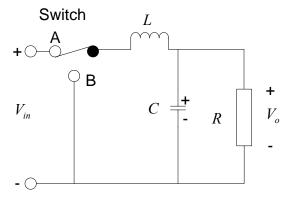

The next step in the evolutionary development of the buck converter is to add a capacitor across the load resistor and this circuit is shown in Figure 10. A capacitor reduces the ripple content in voltage across it, whereas an inductor smoothes the current passing through it. The combined action of LC filter reduces the ripple in output to a very low level.

Figure 10: Circuit with an LC Filter

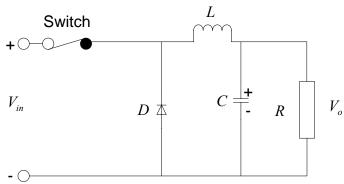

With the circuit in Figure 10 it is possible to have a power semiconductor switch to correspond to the switch in position A and a diode in position B. The circuit that results is shown in Figure 11. When the switch is in position B, the current will pass through the diode. The important thing now is the controlling of the power semiconductor switch.

Figure 11: Buck Converter with load resistor

The circuit in Figure 11 can be regarded as the most elementary buck converter without a feedback. The Buck Converter transfers small packets of energy with the help of a power switch, a diode, and an inductor and is accompanied by an output filter capacitor and input filter. All the other topologies such as the Boost, Buck-Boost Converter etc, vary by the different arrangement of these basic components.

This circuit can be further modified by adding the feedback part which is integral for a SMPS because based on the feedback it stabilizes the output. Such a circuit is shown in the Figure 12.

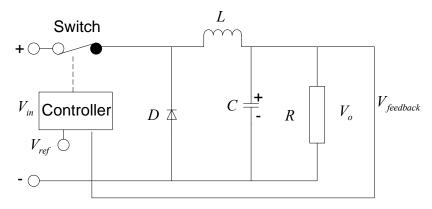

Figure 12: Step Down Switch Mode Power Supply

The PWM Controller (Figure 12) compares a portion of the rectified dc output with a voltage reference ( $V_{ref}$ ) and varies the PWM duty cycle to maintain a constant dc output voltage. If the output voltage wants to increase, the PWM lowers its duty cycle to reduce the regulated output, keeping it at its proper voltage level. Conversely, if the output voltage tends to go down, the feedback causes the PWM duty cycle to increase and maintain the proper output. A buck converter or step-down switch mode power supply can also be called a switch mode regulator [21].

# 3.2 Purpose of different components in the Buck Converter

As just seen in the previous section that any basic switched power supply consists of five standard components:

- pulse-width modulating controller

- transistor switch (active switch)

- inductor

- capacitor

- diode (passive switch)

Now we will look into more detail as to the selection and the functioning of these components.

## **3.2.1 Switch**

In its crudest form a switch can be a toggle switch which switches between supply voltage and ground. But for all practical applications which we shall consider we will deal with transistors. Transistors chosen for use in switching power supplies must have fast switching times and should be able to withstand the voltage spikes produced by the inductor. The input on the gate of the transistor is normally a Pulse Width Modulated (PWM) signal which will determine the ON and OFF time. Sizing of the power switch is determined by the load current and off-state voltage capability.

The power switch (transistor) can either be a MOSFET, IGBT, JFET or a BJT. Power MOSFETs are the key elements of high frequency power systems such as high-density power Supplies [2]. Therefore MOSFETs have now replaced BTJ's in new designs operating at much higher frequencies but at lower voltages. At high voltages MOSFETs still have their limitations. The intrinsic characteristics of the MOSFET produce a large on-resistance which increases excessively when the devices' breakdown voltage is raised. Therefore, the power MOSFET is only useful up to voltage ratings of 500V and so is restricted to low voltage applications or in two-transistor forward converters and bridge circuits operating off-line. At high breakdown voltages (>200V) the on-state voltage drop of the power MOSFET becomes higher than that of a similar size bipolar device with similar voltage rating. This makes it more attractive to use the bipolar power transistor at the expense of worse high frequency performance [28]. As improvements in fabrication techniques, new materials, device characteristics take place than MOSFETs are likely to replace BJTs.

Another new device likely to displace the BJT in many high power applications is the Insulated Gate Bipolar Transistor (IGBT). This device combines the low power drive characteristics of the MOSFET with the low conduction losses and high blocking voltage characteristics of the BJT. Therefore the device is highly suited to high power, high voltage applications. However, since current transport in the

device is by the same process as the BJT, its switching speed is much slower than the MOSFET, so the IGBT is at present limited to lower (<50kHz) applications [31].

# **Operating Frequency**

The operating frequency determines the performance of the switch. Switching frequency selection is typically determined by efficiency requirements. There is now a growing trend in research work and new power supply designs in increasing the switching frequencies. The higher is the switching frequency, the smaller the physical size and component value. The reason for this is to reduce even further the overall size of the power supply in line with miniaturisation trends in electronic and computer systems.

However, there is an upper frequency limit where either magnetic losses in the inductor or switching losses in the regulator circuit and power MOSFET reduce efficiency to an impractical level. Higher frequency also reduces the size of the output capacitor. E.g., the capacitance required is  $67\mu F$  at 500 KHz, but only  $33\mu F$  at 1MHz. The ripple current specification remains unchanged [24].

#### 3.2.2 Inductor

The function of the inductor is to limit the current slew rate (limit the current in rush) through the power switch when the circuit is ON. The current through the inductor cannot change suddenly. When the current through an inductor tends to fall, the inductor tends to maintain the current by acting as a source. This limits the otherwise high-peak current that would be limited by the switch resistance alone. The key advantage is when the inductor is used to drop voltage, it stores energy. Also the inductor controls the percent of the ripple and determines whether or not the circuit is operating in the continuous mode.

Peak current through the inductor determines the inductor's required saturationcurrent rating, which in turn dictates the approximate size of the inductor. Saturating the inductor core decreases the converter efficiency, while increasing the temperatures of the inductor, the MOSFET and the diode. The size of the inductor and capacitor can be reduced by the implementation of high switching frequency, multi-phase interleaved topology, and a fast hysteric controller [30].

A smaller inductor value enables a faster transient response; it also results in larger current ripple, which causes higher conduction losses in the switches, inductor, and parasitic resistances. The smaller inductor also requires a larger filter capacitor to decrease the output voltage ripple.

Inductors used in switched supplies are some times wound on toroidal cores, often made of ferrite or powdered iron core with distributed air-gap to store energy.

A DC-DC converter transfers energy at a controlled rate from an input source to an output load, and as the switching frequency increases, the time available for this energy transfer decreases. For example, consider a buck converter operating at 500 kHz with a 10 μH inductor. For most DC-DC converters, changing the frequency to 1 MHz allows use of exactly one half the inductance, or 5μH.

## 3.2.3 Capacitor

Capacitor provides the filtering action by providing a path for the harmonic currents away from the load. Output capacitance (across the load) is required to minimize the voltage overshoot and ripple present at the output of a step-down converter. The capacitor is large enough so that its voltage does not have any noticeable change during the time the switch is off. Large overshoots are caused by insufficient output capacitance, and large voltage ripple is caused by insufficient capacitance as well as a high equivalent-series resistance (ESR) in the output capacitor. The maximum allowed output-voltage overshoot and ripple are usually specified at the time of design. Thus, to meet the ripple specification for a step-down converter circuit, we must include an output capacitor with ample capacitance and low ESR.

The problem of overshoot, in which the output-voltage overshoots its regulated value when a full load is suddenly removed from the output, requires that the output capacitor be large enough to prevent stored inductor energy from launching the output above the specified maximum output voltage.

Since switched power regulators are usually used in high current, high-performance power supplies, the capacitor should be chosen for minimum loss. Loss in a capacitor occurs because of its internal series resistance and inductance. Capacitors for switched regulators are partly chosen on the basis of Effective Series Resistance (ESR). Solid tantalum capacitors are the best in this respect [9]. For very high performance power supplies, sometimes it is necessary to parallel capacitors to get a low enough effective series resistance.

## 3.2.4 Freewheeling Diode/Transistor

Since the current in the inductor cannot change suddenly, a path must exist for the inductor current when the switch is off (open). This path is provided by the freewheeling diode (or catch diode).

The purpose of this diode is not to rectify, but to direct current flow in the circuit and to ensure that there is always a path for the current to flow into the inductor. It is also necessary that this diode should be able to turn off relatively fast. Thus the diode enables the converter to convert stored energy in the inductor to the load. This is a reason why we have higher efficiency in a DC-DC Converter as compared to a linear regulator. When the switch closes, the current rises linearly (exponentially if resistance is also present). When the switch opens, the freewheeling diode causes a linear decrease in current. At steady state we have a saw tooth response with an average value of the current.

In many circuits and the one we will be discussing such as the Synchronous Buck Converter we will see that the Freewheeling diode is replaced by the Negative Field Effect Transistor (NFET). The reasons for this in short are to increase the efficiency. The 0.7 V forward voltage drop (or a little less with a Schottky diode) is a main source of efficiency loss in the buck regulator at low voltages. An alternative is to use a transistor in saturation (0.2V or 0.3V) to provide the flywheel function. This arrangement does raise some complications because the buck regulator has to synchronously turn on the flywheel element at just the right times, in order to keep the current flowing smoothly. The diode solution turns itself on and off, so it does not require a synchronous flywheel drive signal. The active circuit with the synchronous flywheel transistor is generally more expensive than the simple passive diode circuit, but the gain in efficiency (P<sub>out</sub>/P<sub>in</sub>) is sometimes worth the extra cost. But in any case we have a Schottky in parallel with the flywheel transistor, rather than a Zener. A well saturated transistor will have a lower V<sub>ds</sub> than the Schottky diode, but the diode will help ease/guarantee the switching transition.

#### 3.2.5 Feedback

Feedback and control circuitry can be carefully nested around these circuits to regulate the energy transfer and maintain a constant output within normal operating conditions. Control by pulse-width modulation is necessary for regulating the output. The transistor switch is the heart of the switched supply and it controls the power supplied to the load. More of this will be discussed in Chapter 4.

# 3.3 States of Operation

There are two states in which the circuit given in Figure 13 operates. That is the ON State and the OFF State. These two states and the active circuit part for those given states are shown in the Figure 14 & Figure 15.

Figure 13: General Buck Converter Schematic

#### **3.3.1 ON State**

The operation of the buck converter is fairly simple, with an inductor and two switches (usually a transistor and a diode) that control the inductor. It alternates between connecting the inductor to source voltage to store energy in the inductor and discharging the inductor into the load.

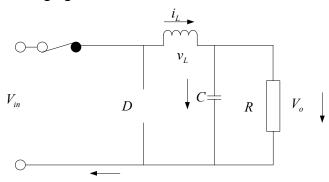

Figure 14: ON State

Refer to Figure 14, when the switch is connected, L is connected to the switch which tends to oppose the rising current and begins to generate an electromagnetic field in its core. Diode D is reverse biased and is essentially an open circuit at this point. The inductor current increases, inducing a positive voltage drop across the inductor and a lower output supply voltage in reference to the input source voltage. The inductor serves as a current source to the output load impedance.

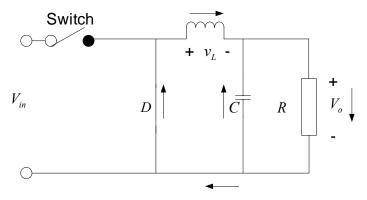

### 3.3.2 OFF State

Figure 15: OFF State

In the OFF state the switch is open, diode D conducts and energy is supplied from the magnetic field of L and electric field of C. The current through the inductor falls linearly. When the FET switch is off, the inductor current discharges, inducing a negative voltage drop across the inductor. Because one port of the inductor is tied to ground, the other port will have a higher voltage level, which is the target output supply voltage. The output capacitance acts as a low-pass filter, reducing output voltage ripple as a result of the fluctuating current through the inductor. The diode prevents the current flowing from the inductor when the FET switch is off.

#### 3.3.3 Continuous Mode / Discontinuous Mode

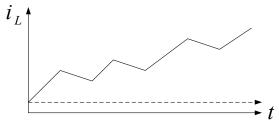

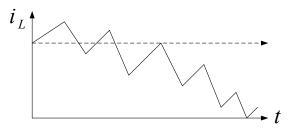

During the ON state and than the subsequent OFF state the Buck Converter can operate in Continuous Mode or Discontinuous Mode. The difference between the two is that in CCM the current in the inductor does not fall to zero. See Figure 16

Figure 16: (a) Continuous Mode (b) Discontinuous Mode

Current flows continuously in the inductor during the entire switching cycle in steady state operation. In most Buck regulator applications, the inductor current never drops to zero during full-load operation. Overall performance is usually better using continuous mode, and it allows maximum output power to be obtained from a given input voltage and switch current rating. Energy from the battery is supplying the load and is being stored in the inductor L as a magnetic field. The current through the inductor is rising linearly.

In the DCM the current in the inductor falls to zero and remains at zero for some portion of the switching cycle. It starts at zero, reaches a peak value, and returns to zero during each switching cycle. In applications where the maximum load current is fairly low, it can be advantageous to design for discontinuous mode operation. In these cases, operating in discontinuous mode can result in a smaller overall converter size (because a smaller inductor can be used). Often the output capacitor must be large to keep the voltage constant.

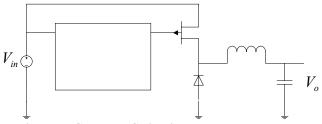

## 3.4 Synchronous Buck Converters

#### 3.4.1 Introduction

Synchronous buck converters have received great attention for low-voltage power conversion because of its high efficiency and reduced area consumption [4]. One of the main reasons for not using a synchronous FET earlier was that there was a much greater cost difference between FETs and Schottky diodes years ago. Moreover, since output voltages were generally higher (5V or greater), the drop across the Schottky was not as large a percentage as it is now. As FET technology has improved, providing better and better conductivity at ever lower price, the FET has become the main choice over the Schottky. Even more importantly, the "forward" voltage drop of the FET can be arbitrarily low compared to the Schottky a major issue with output voltages hovering around 1 volt. The synchronous buck topology is also considered suitable for Envelope Tracking Power Supply because of its simple dynamics and symmetrical slew-rate capability [6].

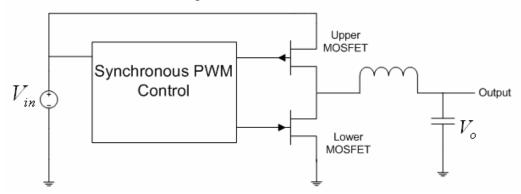

## 3.4.2 Topology

This topology uses the complementary switches (Figure 17) to transfer energy to the filter inductance from the power source.

Figure 17: Complementary switches

The synchronous buck converter is essentially the same as the buck step-down converter with the substitution of the "catch" diode for another FET switch, or Synchronous Rectifier (SR). The upper MOSFET conducts to transfer energy from the input (same as the conventional buck converter) and charges the inductor current. When the switch control is off, the lower MOSFET switch turns on to circulate the inductor current and provides a current path for the inductor when discharging.

The control and driver circuits synchronize the timing of both MOSFETs with the switching frequency. The synchronous PWM control block regulates the output voltage by modulating the conduction intervals of the upper and lower MOSFETs. This topology improves efficiency with faster switch turn-on time and lower FET series resistance (r<sub>dson</sub>) versus the diode. Under light loads, the control block usually turns the lower MOSFET off to emulate a diode[29], this is because more power is lost in turning a large FET switch on and off, than lost due to the resistance of the switch itself.

## 3.4.3 Improvements

Synchronous rectification increases the efficiency of a buck converter by replacing the Schottky diode with a low-side NMOS FET. The resultant voltage drop across the MOSFET can be smaller than the forward voltage drop of the Schottky diode. To show that the efficiency is greatly increased by replacing the diode with a MOSFET can be shown with the following set of equations. First consider the case when we have a diode. The equation for power loss across a diode can be calculated with Eq. 3-1.

$$P_D = V_D \cdot (1 - D) \cdot I_o$$

(Eq. 3-1)

Note that it is multiplied with (1-D) for the OFF time. Because the diode conducts in the OFF state. Assume that the input is 5V and the output is 3.3 V, and the load current is 10A. In this case the duty cycle will be 66% and the diode will be ON for 34% of the time. A typical diode with a 0.7V would suffer a power loss of 2.38 W.

Now we take the equation for a switch

$$P_{S2} = I_o^2 \cdot R_{DSON} \cdot (1 - D)$$

(Eq. 3-2)

It can be seen that the power loss is very much dependent upon the duty cycle. A synchronous rectifier generally has lower losses than a conventional or Schottky diode, and so its use is quite popular in low voltage DC/DC converters. Also for increased efficiency the following relation must be true  $I_o^2 \cdot R_{DSON} \ll V_D$ .

#### 3.4.4 Problems

This topology requires more components and additional switch logic sequencing. Also this power conversion topology suffers from a degraded

efficiency at light loads [32] (because power is lost in turning on the device), a problem that can severely limit the battery lifetime of portable devices that spend a substantial amount of time in "stand-by" mode and hence resulting in a substantial reduction in converter efficiency. Since many portable devices operate in low-power standby modes for a majority of the time they are on, increasing light-load converter efficiency can significantly increase battery lifetime. The SRBC requires two off-chip passive filter components. These components greatly increase the overall size and cost of the system.

Synchronous rectification with discrete MOSFETs causes variable switching delays because of the variations in gate charge and threshold voltage from one MOSFET to another. Standard control circuits compensate for these variations by delaying the turn-on drive of the lower MOSFET until after the gate voltage of the upper MOSFET falls below a threshold. This delay creates a dead time in which neither MOSFET conducts. The dead time eliminates the possibility of a destructive shoot-through condition in which both MOSFETs conduct simultaneously. Standard designs use the same method to delay the turn-on of the upper device [29].

## 4. Practical Issues of Buck Converter

In the previous chapter we looked at the working of the Buck Converter. In this chapter we will derive the equations for practical calculations.

# 4.1 Calculation for Duty Ratio

For calculation of the duty ratio we will first of all assume that the converter is in steady state. (For steady state see Appendix C). The switches are treated as being ideal, and the losses in the inductive and the capacitive elements are neglected. Also it is important to point out that the following analysis does not include any parasitic resistances (all ideal case). The analysis also has the assumption that the converter is operating in Continuous conduction mode only i.e.  $i_L(t) > 0$ .

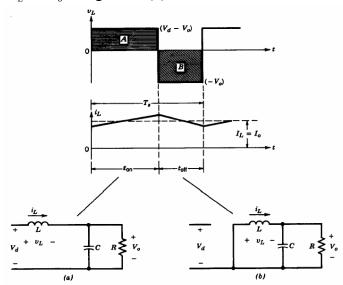

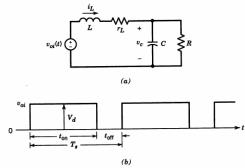

When the switch is on for time duration  $t_{on}$ , the switch conducts the inductor current and the diode becomes reverse biased. This results in a positive voltage  $v_L = V_d - V_o$  across the inductor in Figure 18(a). This voltage causes a linear increase in the inductor current  $i_L$ . When the switch is turned off, because of the inductive energy storage,  $i_L$  continues to flow. This current now flows through the diode, and  $v_L = -V_o$  in Figure 18 (b).

Figure 18: Step-down converter circuit states (assuming  $i_L$  flows continuously): (a) switch on; (b) switch off [1]

Since in steady-state operation waveform must repeat from one time period to the next, the integral of the inductor voltage  $v_L$  over one time period must be zero, where  $T_s = t_{on} + t_{off}$ :

$$\int_{0}^{T_{s}} v_{L} dt = \int_{0}^{t_{on}} v_{L} dt + \int_{t_{on}}^{T_{s}} v_{L} dt = 0$$

(Eq. 4-1)

From Figure 18, it implies that areas A and B must be equal (See Appendix C). Therefore,

$$(V_d - V_o)t_{on} = V_o(T_s - t_{on})$$

(Eq. 4-2)

or

$$\frac{V_o}{V_d} = \frac{t_{on}}{T_s} = D \text{ (duty ratio)}$$

(Eq. 4-3)

Hence in this mode, the voltage output varies linearly with the duty ratio of the switch for a given input voltage and does not depend on any other circuit parameter.

## 4.2 Calculation for Inductor

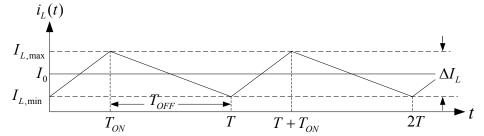

From Figure 18(a) we can derive a simplified differential equation based on the assumption that the voltage across the load, and thereby across the capacitor, is fairly constant. The differential equation in terms of the current through the inductor, when the switch is closed, may now be written as

$$L\frac{di_L(t)}{dt} = V_d - V_o$$

(Eq. 4-4)

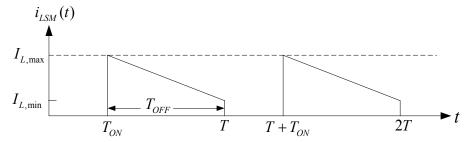

Assuming that the circuit has assumed steady state hence there may already be some current in the inductor,  $I_{L,\min}$ , just prior to the closing of switch S. Hence for a time interval  $0 \le t \le T_{ON} = DT$ , gives:

$$i_L(t) = \frac{V_d - V_o}{I}t + I_{L,\text{min}}$$

(Eq. 4-5)

The inductor current increases linearly with time and attains its maximum value  $I_{L,\max}$  as  $t \to T_{ON} = DT$  such that

$$I_{L,\text{max}} = \frac{V_d - V_o}{I_L} DT + I_{L,\text{min}}$$

(Eq. 4-6)

Defining the change in the current from its minimum to maximum value as the peak-to-peak current ripple  $\Delta I_L$ , the equation 4-6 yields an expression for  $\Delta I_L$ , as

$$\Delta I_L = I_{L,\text{max}} - I_{L,\text{min}} = \frac{V_d - V_o}{L} DT$$

(Eq. 4-7)

Note that the current ripple is directly proportional to D, the duty cycle, upon which we may not have any control because of the output voltage requirement. However, it is inversely proportional to the inductance L upon which we can exert some control. Thus, the current ripple can be controlled by a proper selection of the inductor.

Let us now analyze the circuit when the switch is in its open position. The inductor current completes its path through the lower side MOSFET and the corresponding differential equation, for  $0 \le t \le T_{OFF}$ , is

$$L\frac{di_L(t)}{dt} = -V_o (Eq. 4-8)$$

From the solution of the above first-order differential equation, we obtain

$$i_L(t) = -\frac{V_o}{L}t + I_{L,\text{max}}$$

(Eq. 4-9)

Where  $I_{L,\max}$  is the maximum value of the current in the inductor at the opening of the switch or the beginning of the off period. As  $t \to T_{OFF} = (1-D)T$ , the inductor current decreases to its minimum value  $I_{L,\min}$  such that

$$I_{L,\text{min}} = -\frac{V_o}{L}(1-D)T + I_{L,\text{max}}$$

(Eq. 4-10)

The Eq. 4-10 yields another expression for the peak-to-peak current ripple as

$$\Delta I_L = I_{L,\text{max}} - I_{L,\text{min}} = \frac{V_o}{L} (1 - D)T$$

(Eq. 4-11)

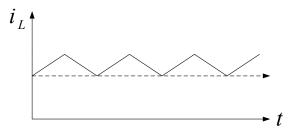

**Figure 19: Inductor Current**

The current through the inductor as given by Eq. 4-5 during the on time and by Eq. 4-9 during the off time is sketched in the Figure 19. The average current in the inductor must be equal to the dc current through the load. That is,

$$I_{L,avg} = I_o = \frac{V_o}{R}$$

(Eq. 4-12)

The expressions for the maximum and minimum currents through the inductor may now be written as

$$I_{L,\text{max}} = I_{L,avg} + \frac{\Delta I_L}{2} = \frac{V_o}{R} + \frac{V_o}{2L} (1 - D)T$$

(Eq. 4-13)

$$I_{L,\text{min}} = I_{L,avg} - \frac{\Delta I_L}{2} = \frac{V_o}{R} - \frac{V_o}{2L} (1 - D)T$$

(Eq. 4-14)

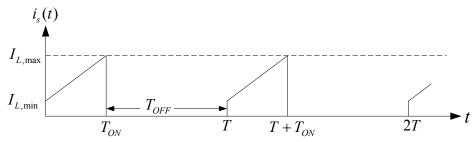

The current supplied by the source varies from  $I_{L,\min}$  to  $I_{L,\max}$  during the time the switch is closed and is zero otherwise as shown in Figure 20.

Figure 20: The source current

When the switch, the inductor, and the capacitor are treated as ideal elements, the average power dissipated by them is zero. Consequently, the average power supplied by the source must be equal to the average power delivered to the load. That is,

$$V_d I_d = V_o I_o = D V_S I_o$$

(Eq. 4-15)

This equation helps us express the average source current in terms of the average load current as

$$I_S = DI_o$$

(Eq. 4-16)

The current through the lower side MOSFET is shown in Figure 21. Its average value is

$$I_{LS} = (1 - D)I_o$$

(Eq. 4-17)

Figure 21: Current through the low side MOSFET

We know the fact that the buck converter can either operate in its continuous conduction mode or discontinuous mode. When it operates in the continuous conduction mode, there is always a current in the inductor. The minimum current in the continuous conduction mode can be zero. Consequently, there is a minimum value of the inductor that ensures its continuous conduction mode. It can be obtained from Eq. 4-14 by setting  $I_{L,\min}$  to zero as

$$\frac{V_o}{R} - \frac{V_o}{2L_{\min}} (1 - D)T = 0$$

(Eq. 4-18)

Hence,

$$L_{\min} = \frac{1 - D}{2}RT = \frac{1 - D}{2f}R$$

(Eq. 4-19)

## 4.3 Calculation for Capacitor

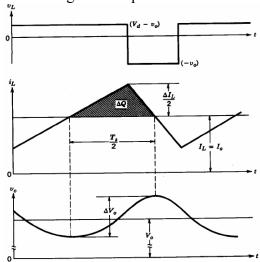

The output capacitor is assumed to be so large as to yield  $v_o(t) = V_o$ . However, the ripple in the output voltage with a practical value of capacitance can be calculated by considering the waveforms shown in Figure 22 for a continuous-conduction mode of operation. Assuming that all of the ripple component in  $i_L$  flows through the capacitor and its average component flows through the load resistor, the shaded area in Figure 22 represents an additional charge  $\Delta Q$ .

Figure 22: Output voltage ripple in a step-down converter

Therefore, the peak-to-peak voltage ripple  $\Delta V_o$  can be written as

$$\Delta V_o = \frac{\Delta Q}{C} = \frac{1}{C} \frac{1}{2} \frac{\Delta I_L}{2} \frac{T_s}{2}$$

(Eq. 4-20)

From Figure 22 during  $t_{off}$

$$\Delta I_L = \frac{V_o}{L} (1 - D) T_s$$

(Eq. 4-23)

Therefore, substituting  $\Delta I_L$  from Eq. 4-23 into the Eq. 4-20 gives

$$\Delta V_o = \frac{T_s}{8C} \frac{V_o}{L} (1 - D) T_s$$

(Eq. 4-24)

$$\therefore \frac{\Delta V_o}{V_o} = \frac{1}{8} \frac{T_s^2 (1 - D)}{LC} = \frac{\pi^2}{2} (1 - D) \left(\frac{f_c}{f_s}\right)^2$$

(Eq. 4-25)

Where switching frequency  $f_s = 1/T_s$  and

$$f_c = \frac{1}{2\pi\sqrt{LC}}$$

(Eq. 4-26)

Equation 4-25 shows that the voltage ripple can be minimized by selecting a corner frequency  $f_c$  of the low pass filter at the output such that  $f_c \ll f_s$ . Also, the ripple is independent of the output load power, so long as the converter operates in the continuous-conduction mode. We should note that in switch-mode dc power supplies, the percentage ripple in the output voltage is usually specified to be less than, for instance, 1%.

The analysis carried out above assumes ideal components and if we were to make the analysis using all the non-ideal components it would make the derivation a bit more complex with a lot of other parameters included in the final equation. But for the calculation of initial values of the components the above approximations does result in reasonable values. It is also important to realize here that the ESR and ESL are also important and can even dominate. More about how the non-ideality can affect the overall system can be found on [21].

### 4.4 PWM Controller

The heart of a switching power supply is its switch control circuit (controller). One of the key objectives in designing a controller for the power converter is to obtain tight output voltage regulation under different line and load conditions [7]. Often, the control circuit is a negative-feedback control loop connected to the switch through a comparator and a Pulse Width Modulator (PWM). The switch control signal (PWM), controls the state (on or off) of the switch. This control circuit regulates the output voltage against changes in the load and the input voltage.

#### 4.4.1 PWM

PWM is the method of choice to control modern power electronics circuits. The basic idea is to control the duty cycle of a switch such that a load sees a controllable average voltage. To achieve this, the switching frequency (repetition frequency for the PWM signal) is chosen high enough that the load

cannot follow the individual switching events and they appear just a "blur" to the load, which reacts only to the average state of the switch (later on in this chapter the State Space Averaging Method will be introduced).

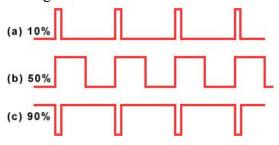

With pulse-width modulation control, the regulation of output voltage is achieved by varying the duty cycle of the switch, keeping the frequency of operation constant. Duty cycle refers to the ratio of the period for which the power semiconductor is kept ON to the cycle period. A clearer understanding can be acquired by the Figure 23.

Figure 23: PWM Signal

The Figure 23 shows PWM signals for 10% (a), 50% (b), and 90% (c) duty cycles. Usually control by PWM is the preferred method since constant frequency operation leads to optimization of LC filter and the ripple content in output voltage can be controlled within the set limits.

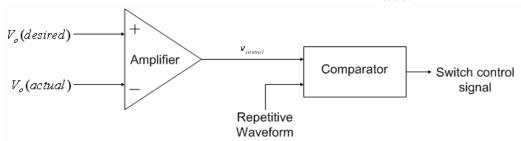

## 4.4.2 Comparator and Voltage to PWM Converter

Switching power supplies rely on negative feedback to maintain the output voltages at their specified value. To accomplish this, a differential amplifier is used to sense the difference between an ideal voltage (the reference voltage) and the actual output voltage to establish a small error signal ( $v_{control}$ ).

Figure 24: Voltage Reference Comparator [1]

The PWM switching at a constant switching frequency is generated by comparing a signal-level control voltage  $v_{control}$  with a repetitive waveform as shown in Figure 24.

Figure 25: PWM Comparator Signals [1]

The frequency of the repetitive waveform with a constant peak, which is shown to be a sawtooth, establishes the switching frequency. This frequency is kept constant in a PWM control and is chosen to be in a few hundred kilohertz range. When the amplified error signal, which varies very slowly with time relative to the switching frequency, is greater than the sawtooth waveform, the switch control signal becomes HIGH, causing the switch to turn on. Otherwise, the switch is off. So when the circuit output voltage changes,  $v_{control}$  also changes causing the comparator threshold to change. Consequently, the output pulse width also changes. This duty cycle change then moves the output voltage to reduce to error signal to zero, thus completing the control loop. In terms of  $v_{control}$  and the peak of the sawtooth waveform  $V_{st}$  in Figure 25, the switch duty ratio can be expressed as

$$D = \frac{t_{on}}{T_s} = \frac{v_{control}}{v_{st}}$$

(Eq. 4-27)

# 4.5 Feedback Control System

As has been mentioned earlier as well that the output voltages of dc power supplies are regulated to be within a specified tolerance band (e.g.,  $\pm 1\%$  around its nominal value) in response to changes in the output load and the input

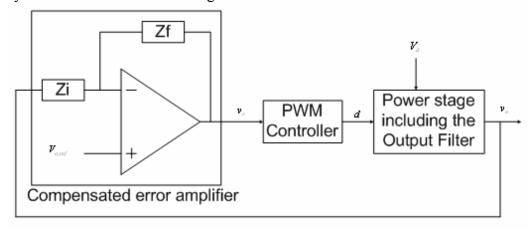

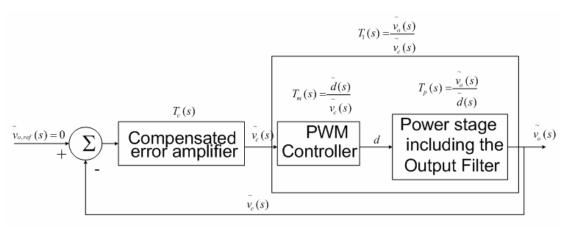

voltage lines. This process is accomplished by employing a negative feedback system which can be seen in Figure 26.

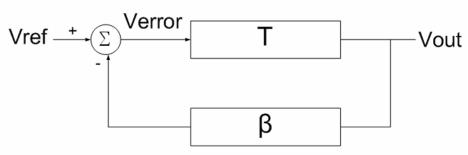

Figure 26: Feedback Control System [1]

The Power stage of the switch converter is not linearized. Since nonlinear systems are not equal to the sum of their parts, they are often difficult (or impossible) to model, and their behaviour with respect to a given variable (for example, time) is extremely difficult to predict. When modelling non-linear systems, therefore, it is common to approximate them as linear, where possible.

With the Linear model, it will make possible certain mathematical assumptions and approximations, allowing for simple computation of results. In nonlinear systems these assumptions cannot be made.

If the power stage of the switch-mode converter in Figure 26 can be linearized, then the Nyquist stability criterion and the Bode plots can be used to determine the appropriate compensation in the feedback loop for the desired steady-state and transient response. Each block in Figure 26 can be linearized around a steady-state operating point as using the state-space averaging technique [5] which allowed the theoretical prediction of a converters frequency response, and therefore a better understanding of a switched-mode regulator's feedback loop and stability criteria. This technique was developed by R. D. Middlebrook at Power Electronics Group - California Institute of Technology, USA. Therefore, each block in Figure 26 can be represented by a transfer function as shown in Figure 27, where the small ac signals are represented by "~."

Figure 27: Linearized Feedback Control System [1]

# 4.6 Linearization using State-Space Averaging

The goal of the following analysis is to obtain a small signal transfer function  $\tilde{v_o}(s)/\tilde{d}(s)$ , where  $\tilde{v_o}$  and  $\tilde{d}$  are small perturbations in the output voltage  $v_o$  and the switch duty ratio d, respectively, around their steady-state dc operating values  $V_o$  and D [1].

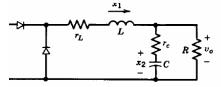

## 4.6.1 Power Stage & Output Filter

**Step 1 State-Variable Description for Each Circuit State.** In a converter operating in a continuous-conduction mode, there are two circuit states: one state corresponds to when the switch is on and the other to when the switch is off. A third circuit state exists during the discontinuous interval, which is not considered in the following analysis because of the assumption of a continuous-conduction mode of operation.

During each circuit state, the linear circuit is described by means of the state-variable vector  $\mathbf{x}$  consisting of the inductor current and the capacitor voltage. In the circuit description, the parasitic elements such as the resistance of the filter inductor and the equivalent series resistance (ESR) of the filter capacitor should also be included. Here  $V_d$  is the input voltage. A lowercase letter is used to represent a variable, which includes its steady-state dc value plus a small ac

perturbation, for example,  $v_o = V_o + v_o$ . Therefore, during each circuit state, we can write the following state equations:

$$\dot{\mathbf{x}} = \mathbf{A}_1 \mathbf{x} + \mathbf{B}_1 v_d \qquad \text{during } d \cdot T_s \qquad (\text{Eq. 4-28})$$

and

$$\mathbf{x} = \mathbf{A}_2 \mathbf{x} + \mathbf{B}_2 \mathbf{v}_d \qquad \text{during } (1 - d) \cdot T_s \qquad \text{(Eq. 4-29)}$$

where  $A_1$  and  $A_2$  are state matrices and  $B_1$  and  $B_2$  are vectors.

The output  $v_o$  in all converters can be described in terms of their state variables alone as

$$v_o = \mathbf{C}_1 \mathbf{x}$$

during  $d \cdot T_s$  (Eq. 4-30)

and

$$v_o = \mathbf{C}_2 \mathbf{x}$$

during  $(1 - d) \cdot T_s$  (Eq. 4-31)

where  $C_1$  and  $C_2$  are transposed vectors.

**Step 2 Averaging the State-Variable Description Using the Duty Ratio** *d***.** To produce an average description of the circuit over a switching period, the equations corresponding to the two foregoing states are time weighted and averaged, resulting in the following equations:

$$\dot{\mathbf{x}} = [\mathbf{A}_1 d + \mathbf{A}_2 (1 - d)] \mathbf{x} + [\mathbf{B}_1 d + \mathbf{B}_2 (1 - d)] \mathbf{v}_d$$

(Eq. 4-32)

and

$$v_o = [\mathbf{C}_1 d + \mathbf{C}_2 (1 - d)] \mathbf{x}$$

(Eq. 4-33)

Step 3: Introducing Small ac Perturbations and Separation into ac and dc Components. Small ac perturbations, represented by "~", are introduced in the dc steady-state quantities (which are represented by the upper case letters). Therefore,

$$\mathbf{x} = \mathbf{X} + \mathbf{x} \tag{Eq. 4-34}$$

$$v_o = V_0 + v_o$$

(Eq. 4-35)

and

$$d = D + d$$

(Eq. 4-36)

In general,  $v_d = V_d + v_d$ . However, in view of our goal to obtain the transfer

function between voltage  $v_o$  and the duty ratio d, the perturbation  $v_d$  is assumed to be zero in the input voltage to simplify our analysis. Therefore

$$v_d = V_d \tag{Eq. 4-37}$$

Using Eq. 4-34 through 4-37 in Eq 4-32 and recognizing that in steady state,  $\dot{\mathbf{X}} = 0$ ,

$\dot{\tilde{\mathbf{x}}} = \mathbf{A}\mathbf{X} + \mathbf{B}V_d + \mathbf{A}\tilde{\mathbf{x}} + \left[ (\mathbf{A}_1 - \mathbf{A}_2)\mathbf{X} + (\mathbf{B}_1 - \mathbf{B}_2)V_d \right] \tilde{d} + \text{terms containing products}$ of  $\tilde{\mathbf{x}}$  and  $\tilde{d}$  (to be neglected) (Eq. 4-38)

where

$$A = A_1 D + A_2 (1 - D)$$

(Eq. 4-39)

and

$$\mathbf{B} = \mathbf{B}_1 D + \mathbf{B}_2 (1 - D)$$

(Eq. 4-40)

The steady-state equation can be obtained from Eq. 4-38 by setting all the perturbation terms and their derivatives to zero. Therefore, the steady-state equation is

$$\mathbf{AX} + \mathbf{B}V_d = 0 \tag{Eq. 4-41}$$

and therefore in Eq. 4-38

$$\dot{\tilde{\mathbf{x}}} = \mathbf{A} \, \tilde{\mathbf{x}} + \left[ (\mathbf{A}_1 - \mathbf{A}_2) \mathbf{X} + (\mathbf{B}_1 - \mathbf{B}_2) V_d \right] \tilde{d}$$

(Eq. 4-42)

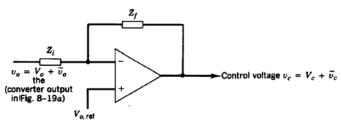

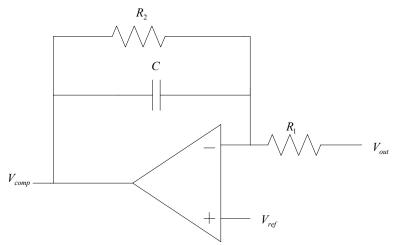

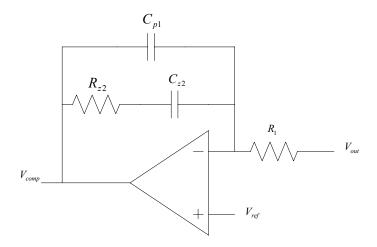

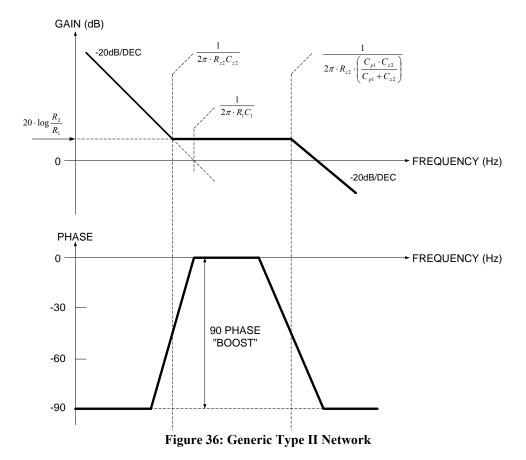

Similarly, usings Eqs. 4-34 to 4-36 in Eq. 4-33 results in