|

|

Forum Index : Electronics : Random Unexplained Inverter Failures

| Author | Message | ||||

| Solar Mike Guru Joined: 08/02/2015 Location: New ZealandPosts: 1203 |

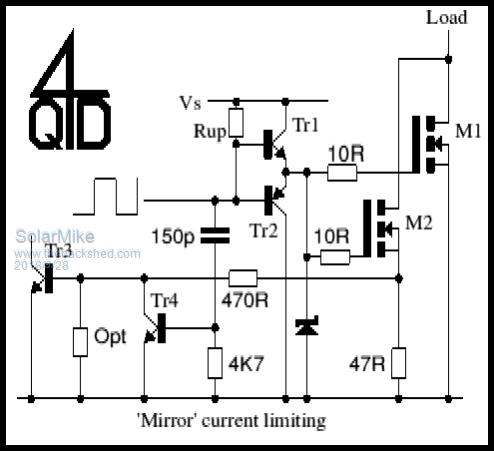

Here is an example of using a current mirror to sense current drawn from a single mosfet, this could be one of the lower devices in the H-Bridge. The on resistance of the Main load mosfet (M1) has a very small voltage developed across it due to its load current, this current is mirrored by the second device (M2) and is sensed as a much higher voltage across the 47r load by TR3. Something like this could be used to sense abnormal currents at the 23Khz switching rate and shutdown the drive. Normally current mirrors require matched devices usually on the same silicon, however we do not require absolute accuracy, just an extreme overload condition, so it should work.  Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

Mike, not sure how well that will work in our particular situation. The voltage developed across M2 and the 47 ohm can never be greater than the drain source saturation voltage developed across M1. For Tr3 to turn on that would need to be something greater than 600mV. Here is a link giving some more details of this mirror measurement method: https://www.onsemi.com/pub/Collateral/AND8093-D.PDF Lets think about this. Current limit set point maybe 25 amps rms in secondary or 35 amps peak. Toroid ratio 9:1 Peak current in primary 315 amps. If there are four HY4008 mosfets, say 79 amps per mosfet. If the Rds on of a HY4008 is perhaps 2.9 milliohms that gives us 229mV of saturation voltage at 79 amps. It should work if Tr3 was a fast voltage comparator instead of a bipolar transistor. Definitely worth a try. Cheers, ĀTony. |

||||

| Solar Mike Guru Joined: 08/02/2015 Location: New ZealandPosts: 1203 |

Thank's for the link Warp, will have a read. >> Another possible gremlin is gate source capacitance of M2 putting a big current spike into the 47 ohm resistor during M2 turn on. This is blanked by TR4 and the 150p cap at turn on. The cct was only a suggestion, TR3 would be in our situation be replaced by a comparator with a settable reference voltage for the trip point. Many of those Chinese inverters use a sense resistor, 3 or 4 parallel wires on the main pcb in one leg to detect over current, that's not the best as they heat up, we need sensing in both legs, so 2 extra mosfets and a dual comparator. I think I have convinced myself to try this out. Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

Yup. Sounds good Mike. You might also like to take a look at a Motorola MC33153 IGBT gate driver chip that has a number of relevant features that may be adaptable. https://www.onsemi.com/pub/Collateral/MC33153-D.PDF Cheers, ĀTony. |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

More random thoughts......Warp and Mike thanks for the input and discussion. But is it time to play devils advocate again and derail our current thoughts for a bit. If we were designing a commercial product from scratch we would probably start with a fast DSP and go in the direction we've been discussing of protecting the FET power circuitry to the highest degree we could. However lets consider the current approach a bit more. What are we trying to build and why. A low cost reliable agricultural inverter with a large overload capability that people can duplicate with a modest skill set, equipment and budget. We want it to avoid self destruction within reason. For instance when was the last time you shorted your mains out with something you shouldn't have? If that resulted in a new set of FETs is it a proportional penalty to pay for what happened? Maybe the approach of ensuring orderly startup and shutdown and elimination of any glitches pulses etc we dont want is the best approach in the spirit of this forum. In other words make the controller board behave in the best manner we can by eliminating evils of the 8010 and maybe random failures will be reduced accordingly. Re-visit the output stage (including the correct choke) and make sure we have the right configuration and values used for best performance and reliable operation . I am re-considering just using a mechanical appropriately rated circuit breaker on the AC output, having an AC current sense transformer feedback set to say maybe 4 x overload power to shutdown the inverter - probably latched and just let the rest take care of itself. I will provide for current sense in the output FET stage/s of my design - but it will be an academic exercise and not actually used initially, but allowing me to experiment at a later date if I feel the need. If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

I suppose the very first thing is to have a PWM source that is absolutely clean without any errant behavior in any mode of operation. I am not absolutely certain that any of the Chinese EG boards are completely above suspicion. Next thing is to build the power electronics hardware and interface in such a way that it does not introduce any noise or extra sources of possible failure, especially during power up, power down, and brownout conditions where power supply rails can be in unpredictable and rapidly changing conditions. Third requirement would be complete opto isolation of the power stage from the control system to isolate any catastrophic failures as much as possible, keep noise right out of the control system, and prevent fault escalation if something does go *BANG*. And lastly, some kind of simple reliable overload protection from unfortunate events on the inverter output. With luck, a simple fuse or circuit breaker should be adequate if the rate of fault current rise through the mosfets can be well enough controlled. The whole thing should be kept as simple and basic as possible, easy to assemble, with the minimum of parts, and the parts should be easy to obtain, access and replace. My own philosophy is that the inverter should be a simple robust thing that turns dc into ac. All of the monitoring, data logging, displays, voltage and current protection can be external to the actual inverter itself. Cheers, ĀTony. |

||||

| theoldwizard1 Newbie Joined: 25/09/2018 Location: United StatesPosts: 5 |

From my work in the automotive industry, fuses are ridiculously slow ! They can operate for minutes at 200% of their rating ! Same is true for breakers. They can operate at 1000% of their rating for minutes. The only viable alternative is a current sense transformer or a shunt .  |

||||

| Tinker Guru Joined: 07/11/2007 Location: AustraliaPosts: 1904 |

Thanks for the info and comments about current transformers, that got me thinking that might explain the strange shut downs of my big inverter (I have fixed the brownouts - had too sensitive Lo voltage sensing), but there might have been some collateral damage when the C/t was left unplugged accidentally. Now. I'm using a recycled one like this: C/T Can any of you confirm the 57P1805A should have a 100 Ohm load resistance? Some consideration for wiseguy, before adding elaborate startup protection circuits, consider how mine starts up: 1. the big capacitors are empty 2. the 12V and 5V control voltages come from a DC/DC converter, connected across the incoming DC (big Capacitors). 3. startup is *always* via a load resistor (I use 33R/20W) in the positive DC lead. 4. Turning the big battery C/B on, the caps slowly charge up. 5. as soon as they are up to 5V the 5V rail is on and this, activating the Lo voltage sense, this trips the SCR, effectively shutting down IFB on the EG8010 and SD on the IR2110's. The inverter now *cannot* start up by itself - it *must* be manually reset first. 6. All this happens *before* the caps have charged up to 12V. 7. The caps continue charging and once the Lo V trip voltage is passed (at 48V) a green light comes on at the inverter dash board. I can now reset the EG8010, the red fault light turns off. 8. Now I bridge the 33R load resistor (its on the Battery C/B) and the inverter is ready for switch on. 9. switch on (5V to SPWMEN pin 6) and wait a few seconds. 10. the orange status light turns on and the inverter soft starts. Do you really think more start up protection is required??  Now a word about the shoot through pulses. You may have effectively explained just why we had no problems there by mentioning the slow totem pole transistors we use. I also have rather long gate drive leads (450mm in the big inverter) but they are all exactly the same length - no unequal length tracks on the PCB. But if the modified EG8010 carrier board is working its an easy addition that I might just include - even if its not having to do anything  . .Klaus |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Thank you for the detailed start up explanation Tinker - it did help. I knew the transistor & 3 zener string would shut down the inverter if the battery voltage went too low, but I didn't study it enough to notice that it would also trigger the scr on a slow startup - a good feature. Suppose the EG8010 needed a complete reset due to VFB being out of range for too long can you also talk me through a complete step by step reset/restart procedure to restart the 8010. I can imagine it, discharge the capacitors etc but maybe I might learn something there too. To avoid any confusion re your step 5. as soon as they are up to 5V the 5V rail is on and this, activating the Battery Lo voltage sense ((not mains Lo)) The EG8010 can issue a few other glitches in various conditions even if the inverter enable switch (spwmen)is off. I am looking into a (simple?) startup regime that ensures no glitches or 3 musketeers are ever fed to the FETs. I am still undecided regarding whether I should check the FET driver supply voltages are ok before trying to drive the FETs I intend to use 4 x isolated gate drive supplies (simple but home grown)- so maybe just check 1 voltage ok will suffice. FET drive from the control board will be via fast optos to fully isolate the FET & current circuits from the control PCB. My FET drives will be fast & a glitch wont be forgiven. The data sheet says the CT is for 60Hz and the termination maximum value is 100R. The turns ratio is not specified for the device and the manufacturer has "proprietary" written next to the part number so it is probably made for someone else. As you are using 50Hz, my suggestion would be to check the linearity as follows. Connect a 50R load resistance to the secondary (pins 1 & 2). Feed 2A through a wire passing once through the centre of the CT and check the voltage across the 50R resistor & note it down. If you have 2A through the centre hole and 100mV across the 50R then the secondary current is 2mA and the CT ratio is 1:1000 (2A yields 2mA). Now increase the current to 4A & note the reading. Loop the wire around and pass it again through the centre hole and note the voltage again, and repeat until you have 5 wires passing through the centre. You will have just measured 4A, 8A etc up to 20A. check the linearity of the noted voltages seems reasonable - similar increases across the 50R load for each 4A step. Tell us how it goes. If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Old wizard - agree with the fuses/circuit breakers I have seen fuses almost totally melt a holder whilst passing 140% of rated current for hours. Im still considering exactly what & how the overload will be implemented, maybe depending on the % of overload a timer with warnings could be remotely issued prior to a shut down. Warp thanks for the comments & feedback. I left an EG8010 running in glitch capture mode for 24 hours with no glitches once running - not a totally clean bill of health but showing promise. The scheme used for the EG8010 inverters pwm drive annoys me. It toggles the LHS of the primary between zero & VBatt every half cycle and feeds PWM & inverse PWM in synchronism to make sinewaves. Why not just hold the LHS lower fet at zero and drive the RHS to max and back, them hold the RHS lower FET at zero and PWM the LHS to max and back. The drive is then symmetrical and we dont have a 50V transition occurring on the FETs & between primary and secondary every half cycle. Mains voltage sensing by the EG8010 will still work ok. Its possibly of monumental inconsequence but I will put some gating in my controller to make it work my way! Maybe the mains might have less noise on it.... Does the EG8010 monitor the AC every half cycle or every second half cycle. Assuming it is every half cycle, would a centre tapped secondary FB overwind on the main toroid with 2 diodes for full wave stop flux walking instead of a full bridge circuit which only measures a differential voltage (residual flux could be anywhere)? If the EG8010 is correcting for each half cycle would it help keep the flux centred by making small corrections in the right direction as required ? Is this why the toroid hum noise changes slowly for no apparent reason at times ? If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| Solar Mike Guru Joined: 08/02/2015 Location: New ZealandPosts: 1203 |

The EG8010 has a full bi-polar modulation mode via its link option settings, that would place less stress in the main core, but you will then require 2 chokes in the primary circuit. Doubt if it does any flux management, how can you easily tell without access to its software. Our cores are normally way over spec'd with little or no voltage sag, it would make better sense to feedback a DC battery voltage sample to the 8010 rather than an AC\rectified\delayed voltage. ?? Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

Klaus, That 57P1805A is rated for 20 amps, 100 ohm load, 0.1v per amp, 2v max output. From that we can draw a few conclusions. The 100 ohm load and 2v output means the secondary current will be 20mA. That also agrees with 0.1v per amp, and 2v output equaling 20 amps. Primary current 20 amps, and secondary current 20 mA equals 1,000 turns. Maximum continuous current rating is limited by the recommended temperature rise in the wire to 20mA as its 1,000 turns of very fine wire. Maximum output voltage is limited to 2 volts, anything much higher will drive the magnetic core into a non linear region as it approaches saturation. This is not a hard limit. 2v rms is safe, it will go higher, possibly much higher, but if you stick with 100 ohms and 2v max you cannot go wrong. Cheers, ĀTony. |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

Old Wiz, Quite right about there being a time delay before fuses/circuit breakers open. They are only really designed to protect wiring from burning out. The current ratings can be pretty wide of the mark too. The question is, what limits the safe maximum power of an inverter ? If it uses a large low frequency output transformer, temperature rise in that will limit the continuous output power, but it can take quite large short term surge overloads with ease. What is likely to go bang first are the mosfets. There are two very different possible types of overloads, short term surges lasting a few seconds such as motor starting and inrush currents into various things such as typically fluorescent light ballasts, and switching power supplies with large dc input capacitors. And sudden total dead shorts across the output. In order to get very low conduction losses in our inverter we would normally oversize our mosfets so they can carry several times the normal maximum continuous load safely to cover any reasonable short term surges. Something like that can easily be protected by a fuse or circuit breaker if the design is robust enough, which it has to be anyway for an inverter to be useful with mixed common domestic loads. Now a robust inverter needs to run sweetly and not be under high electrical stress when running under normal loads. Its quite possible that mosfets in a poorly designed inverter are getting pretty rough treatment from some very high peak current spikes which can arise from several different causes. Shoot through or cross conduction is an extreme case, but the mosfet bridge can also see some very large current spikes if its trying to drive a highly capaciative load such as a high ratio step up transformer with a lot of stray (or deliberately added) capacitance across the secondary. There absolutely MUST be a series choke between the mosfet bridge and the transformer primary to get rid of these current spikes. An inverter can appear to be working fine, but may be much more highly stressed than it needs to be, and will be much more prone to blowing up if it has added stress from some really nasty load being connected to it. Much better to get the inverter power stage working robustly than trying to protect something that is by its nature very stressed and fragile. If you have built a bullet proof inverter, a fuse or circuit breaker will very likely be all the protection it needs against a dead short across the output. Nothing at all wrong with adding a very fast over current shutdown, its a very good feature to have. Multiple levels of protection are definitely recommended, but it can never be a substitute for building a really robust inverter in the first place. Cheers, ĀTony. |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

That idea works very well ! Its very fast acting, and can never become unstable as feedback can. If you feed the primary of the transformer with a fixed amplitude 50 Hz sine wave the secondary voltage will only vary very slightly over the entire load range. Its just normal transformer voltage regulation, and the regulation of larger sized transformers is usually excellent. Its just a case of tweaking the PWM output amplitude in exact inverse relationship to the incoming dc voltage. Dead easy ! No PID correction, or slow ramping or stuffing around. Works best if any ac ripple superimposed on the dc supply is averaged out. Inverter output voltage does change with load, but with far less variation than you would see on the grid anyway. Cheers, ĀTony. |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

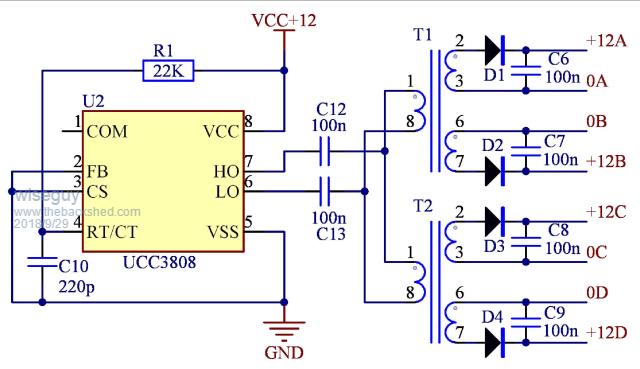

Can we just ignore that its rated at 60Hz? I also would have felt more comfortable if the termination was listed as Typ,100R instead of Max,100R (at 60 Hz?) for those reasons I thought a linearity check might be in order and to go for 1/2 max load? I'm always willing to learn... Another comment about switching the transformer primary from 0 to VBatt every half cycle, the transition is doing what Poida mentioned, which was current glitches caused by Drain to Gate capacitance of the lower FETs coupling the fast + transition back to the gate which tries to turn them on. A solid (low impedance) fast gate drive close to the FETs will normally mitigate this, that is another reason for my preference of a symmetrical drive - Im not convinced their method is the best one - we shall soon find out. I hope to finish my schematic & all PCB's this week, then the fun will really begin. Time to start putting all this stuff into practice. Warp this is my isolated gate power supply circuit, transformer is 1:1:1. In your opinion do I need to check all voltages are ok or check 1 or just assume they are all ok. There does not appear to be an enable in the FET buffer or UVLO (TC4452) - did you do anything special about this?  PS ignore duplicated part numbers - a hazard of copy/paste..... If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| tinyt Guru Joined: 12/11/2017 Location: United StatesPosts: 556 |

Hi wiseguy, in your schematic if the intent is to have +12B and +12D as shown, I think the D2's should be connected like the D1's. Or better: Keep the D2's as shown and re-label the nets: +12B to 0B 0B to +12B +12D to 0D 0D to +12D |

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

Hi Tiny good to hear from you again - thanks for the comments - you noticed my intentional confusion & unintentional confusion you are correct the nets are not labelled correctly. I have used similar circuits many times for this function. Essentially the PWM IC outputs a push pull 12V squarewave and transforms this to the secondary. If it was a flyback circuit the phasing would be wrong. My scheme is a bit mean for the driver IC as there is no current limiting, just the diode and a capacitor. If we do all 4 outputs phased exactly the same way it makes half the push pull driving circuit do all the work. By antiphasing two supply windings it makes the other half of the IC driver do some work also - share the load. I'm always happy to receive comments like this though it has helped avoid an error. On my prototype when I lashed it up I could easily draw ~ 100mA from the one transformer and maintain ~11V - there will also be electrolytics or tantalums ~ 22uF - 47uF for the final circuit.  If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

|

||||

| wiseguy Guru Joined: 21/06/2018 Location: AustraliaPosts: 1267 |

What about circuitry for checking of the isolated voltages - can we forget about running any checking for them ? I will place a zener of no larger than 15V or 16V to each output. Cant hurt - all my testing was done with some load so I didnt see any rise. I plan to use 2 small switchers (buck converters) from the 48V supply. Do we just assume the 5V and 12V main supplies work & are ok or should they be monitored. I want to minimise parts that don't really need to be there ? If at first you dont succeed, I suggest you avoid sky diving.... Cheers Mike |

||||

| Warpspeed Guru Joined: 09/08/2007 Location: AustraliaPosts: 4406 |

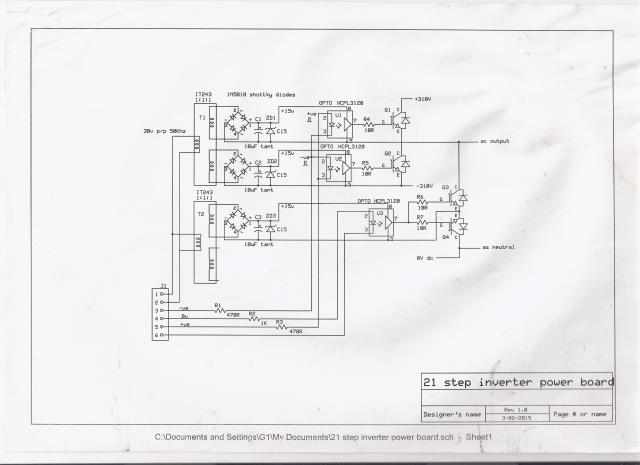

This is an old circuit going back to 2015. It uses a very similar isolated supply concept to yours, its for +15 volts. and ran at 50Khz. The pulse transformers were commercial SCR gate trigger transformers.  The HCPL gate drivers have a built in under voltage shut down with a threshold of around +11v, and this circuit also uses the inverse opto isolator trick for the half bridge part of the circuit. Never had any problems with it blowing up until the crystal oscillator started to give trouble because of shorts between the pads and the crystal's metal can. Other than that it has run reliably powering my house for almost three years, and is still running now. I discovered two things during prototype testing of this circuit. It would not work reliably at +12v, that was too close to the +11v under voltage shut down, so had to wind up the wick to +15v at the 50Khz driver. The other problem was that the +15v supplies were pretty wild going up to almost +20v which was dangerously high for the HCPL3120's. Some 600mW 15v zeners fixed that. And its worked very reliably switching at quite low frequency of course. Cheers, ĀTony. |

||||

| The Back Shed's forum code is written, and hosted, in Australia. | © JAQ Software 2026 |